The TIM generates signals to start fast commands (in the ROD, via the J3 backplane), as well as providing a stand-alone 40.08MHz clock.

Specifically the "Level 1 Trigger" including a 144 clock-period programmable delay, "Bunch Crossing Reset", "Front-End Reset", "Calibration Pulse" sequence, which includes an automatic "Cal. Trigger" after a programmable delay are generated.

These signals are also available on the front-panel as both NIM and ECL signals.

7 registers are responsible for TIM stand-alone operation. A full description of all TIM registers can be found here: (TIM Register List).

0x00 - Enables Register

0x02 - Commands Register

0x04 - Burst Count Register

0x06 - Frequency Register

0x08 - Window Register

0x0A - Delay Register

0x0C - Status Register

In addition, further stand-alone functionality is provided by the Sequencer which is documented in a separate section (see Sequencer Chapter). As its operation bypasses the enables, hierarchy, trigger delays and dead-time limits imposed by the stand-alone system on signals, the Sequencer is not considered part of the TIM stand-alone (aka CLOAC) system.

| BCR | BC (Bunch Crossing) Reset |

| BURST | 'Burst' of a pre set number of Triggers |

| BUSY | Signal Generated or received indicating a busy! |

| CAL | Calibration Test Pulse (with associated Trigger) |

| CLK | Clock usually the 40.08Mhz internal or TTC, but can be anything via the front panel |

| ECR | Event Counter Reset |

| En | (prefix) Enable |

| Ext | (prefix) External - Input from NIM, ECL or IDC(ECL) socket |

| FER | Front End Reset |

| FP | Front-Panel |

| Int | (prefix) Internal (Hardware generated) Clock/Signal |

| OA_Rst | Overall TIM reset |

| TRIG | Level 1 Accept Trigger |

| v | (prefix) VME generated command/signal |

| Win | Window for External Input Trigger |

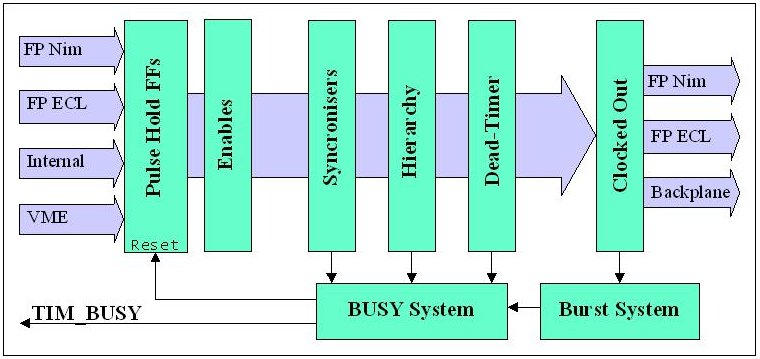

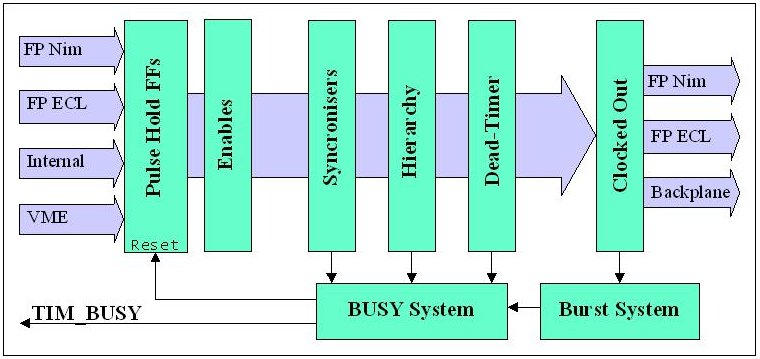

Signals can be generated/introduced via a number of sources: External,

Internal and VME (signals can also be generated by the Sequencer, but this

is documented separately).

The external and internal signals need to be enabled before use in the

Enables Register. VME

signals are actioned directly via the Commands Register.

External (Front-Panel) NIM/ECL Inputs:

These are available for TRIG, CAL, BCR, ECR, FER, SPARE, BUSY, CLKIN

inputs. Currently the SPARE input is configured as a means to start the

Sequencer from an external source. These are can be

enabled using the

Enables Register.

Signals are active on the rising edge only. This allows for detection

of short pulses and prevents long pulses from generating multiple output signals.

Inputs are disabled when the stand-alone system is busy (see

Busy Section).

Internally Hardware Generated:

Two programmable oscillators provide internal triggers, ECRs and FERs.

The frequency is programmable via the

Frequency Register

A counter also provides a stand-alone LHC orbit clock.

Triggers (intTRIGs) are generated at frequencies from 50Hz to 600KHz.

The intTRIG can also be passed through a randomizer. The frequency

remains programmable, but the rate averages a 1/4 of the value selected.

The second oscillator is shared by ECR and FER, and is programable from

0.005Hz to 60Hz.

The internal BCR (intBCR) is generated using the fixed LHC orbit clock (at

frequency of ~11.24kHz).

VME Commands:

All signals can be generated by a bit in the

Commands Register and are edge

triggered (i.e. the command bit used needs to be cleared and set again to send a second signal).

When signals arrive at the TIM stand-alone system (from any source) they are:

Starting with the initial latch, the Internal BUSY is set. This busy can be used if needed (see Busy Operation). Triggers are treated slightly differently as they can be delayed and be required in quick succession (see Trigger Operation).

NOTE: The entire signal chain is cleared during Delay Register writes (see Trigger Operation), as well as when initiating Burst Mode.

Triggers can be delayed using a 144 stage pipeline. The delay is programable via the

Delay Register as a variable tap-off point on the pipeline. For this reason, when the Delay Register is written to, the pipeline is flushed. As this affects other signals, the entire signal processing stream is reset at the same (and the IntBUSY set for the duration).

For predictabilty, it may be better to stop 'running' when changing this setting.

If triggers are delayed, a trigger arriving at the same time as another signal may not clash with it. Accepted triggers, therefore, do not generate a busys. The trigger input is inhibited for a maximum of 3 clocks by a separate input dead-time system that ensures triggers can be generated at the shortest allowed interval.

The delayed-trigger is treated as a normal signal and generates the busy/incoming signal inhibit as expected.

The stand-alone system affects the Internal BUSY (IntBUSY-

Status Register,

masked by enIntBUSY-

Enables Register) in 4 circumstances:

- Input signal has been accepted - waiting prescribed dead-time

- When in Burst Mode Ready state

(see Burst Mode)

- When writing to the Delay Register (see Trigger Operation)

- When a TestBUSY is triggered

All TestBUSY commands are issued via the

Commands Register.

To generate a TestBUSY, set the enTestBUSY. At the next trigger the intBUSY bit will be set, and (if enIntBUSY is set)

the TIM will go BUSY.

To clear this condition, set the ClrTestBUSY bit in the

Commands Register.

For example:

| Enables | Reg00 = 0x0081 | Set enIntBUSY |

| Commands | Reg02 = 0x2000 | Set enTestBUSY |

| Commands | Reg02 = 0x2002 | Generate vTRIG |

| Status | Read Reg0C | Read Status, check 2-IntBUSY, 14-TestBUSY |

| Commands | Reg02 = 0x4000 | Reset TestBUSY bit |

In general, signals arriving via the front panel/VME require synchronisation to the selected clock. Depending on timing, this requires 1 or 2 clks. Signals are also clocked out of the TIM stand-alone module, so this adds 1 more clk.

The trigger requires a little more, as the delay-pipeline has an inherent 2 clk minimum delay.

Latency: TRIG = 4+1 clks, Other signals = 2+1 clks.

The TIM is capable of sending a programmable number of triggers (with or without calibration pulses) in a train or 'burst'.

These triggers are generated as normal via the external or internal sources, including the frequency selectable IntTrig.

To set-up for a burst, the vBurstMode bit is set. This disables all signal sources, with signals in-progress cleared AND the delay pipeline flushed. The internal busy is set.

After setting the vBurstGo bit, Triggers are enabled until the specified number have occurred and then the system will revert to the the all-disabled state described above.

The removal of vBurstMode at anytime will disable the bursting and return the system to normal operation, irrespective of burst status .

Using Burst Mode is best explained with an example:

Enables | Reg00 = 0x0002 |

Use internal trigger |

BurstCount | Reg04 = 0x03FF |

Set Reg04 to the number of triggers in the burst |

Command | Reg02 = 0x0200 |

Set vBurstMode bit - (stops all Triggers) |

| Reg02 = 0x0600 |

Set vBurstGo bit (leaving vBurstMode set) |

Status | Read Reg0C, bit 4 |

Poll the BurstBUSY Status bit until the burst is done |

Command | Reg02 = 0x0200 |

Reset vBurstGo |

| Reg02 = 0x0600 |

Set vBurstGo bit again for second burst |

Status | Read Reg0C, bit 4 |

Poll the BurstBUSY bit until the burst is done |

Command | Reg02 = 0x0000 |

Reset vBurstMode and vBurstGo to return to normal operation |

As it is not possible to generate repetitive CALs internally, a facility is provided whereby the end of a CAL-TRIG generates another CAL. The delay pipeline can be used here to vary the CAL frequency.

NOTE: To use this mode the external CAL inputs MUST be disabled, and a vCAL used to start the loop. In cases where single vCALs need to be generated, setting the enExtCAL bit disables cyclic operation (to ensure unwanted signals don't arrive via to front-panel, unplug the cable!) Example:

Enables | Reg00 = 0x0000 |

Disable all external signals |

BurstCount | Reg04 = 0x03FF |

Set Reg04 to the number of triggers in the burst |

Command | Reg02 = 0x0200 |

Set vBurstMode bit - |

| Reg02 = 0x0600 |

Set vBurstGo bit (leaving vBurstMode set) |

| Reg02 = 0x0610 |

Generate a CAL: Set vCAL bit (leaving vBurstGO, vBurstMode set) |

Status | Read Reg0C, bit 4 |

Poll the BurstBUSY Status bit until the burst is done |

Command | Reg02 = 0x0200 |

Reset vBurstGo |

|

|

|

This is a VME addressed 32k of RAM which can be loaded with a signal sequence set and run in a loop or as a 1-off train. The sequencer is able to control all 8 ***TTCbus*** backplane signals also includes the serial L1ID and TTID bit streams.