ANSI/VITA 1.1-1997

Approved as an American National Standard by

# American National Standard for VME64 Extensions

## Secretariat VMEbus International Trade Association

Approved October 7, 1998 American National Standards Institute, Inc.

## INIEDUS INTERNATIONAL TRADE ASSOCIATIO 7825 E. Gelding Drive, Suite 104, Scottsdale, AZ 85260-3415 PH: 602-951-8866, FAX: 602-951-0720

E-mail: info@vita.com, URL: <u>http://www.vita.com</u>

ANSI/VITA 1.1-1997

American National Standard for VME64 Extensions

### Secretariat VMEbus International Trade Association

Approved October 7, 1998 American National Standards Institute, Inc.

#### Abstract

This standard is an extension of the ANSI/VITA 1-1994, VME64 Standard. It defines a set of features that can be added to VME and VME64 boards, backplanes and subracks. These features include a 160 pin connector, a PO connector, geographical addressing, voltages pins for 3.3V, a test and maintenance bus, and EMI, ESD, and front panel keying per IEEE 1101.10.

## American National Standard

Approval of an American National Standard requires verification by ANSI that the requirements for due process, consensus, and other criteria for approval have been met by the standards developer.

Consensus is established when, in the judgment of the ANSI Board of Standards Review, substantial agreement has been reached by directly and materially affected interests. Substantial agreement means much more than a simple majority, but not necessarily unanimity. Consensus requires that all views and objections be considered, and that a concerted effort be made toward their resolution.

The use of American National Standards is completely voluntary; their existence does not in any respect preclude anyone, whether he has approved the standards or not, from manufacturing, marketing, purchasing, or using products, processes, or procedures not conforming to the standards.

The American National Standards Institute does not develop standards and will in no circumstances give an interpretation of any American National Standard. Moreover, no person shall have the right or authority to issue an interpretation of an American National Standard in the name of the American National Standard Institute. Requests for interpretations should be addressed to the secretariat or sponsor whose name appears on the title page of this standard.

CAUTION NOTICE: This American National Standard may be revised or withdrawn at any time. The procedures of the American National Standards Institute require that action be taken periodically to reaffirm, revise, or withdraw this standard. Purchases of American National Standards may receive current information on all standard by calling or writing the American National Standards Institute.

Published by

#### VMEbus International Trade Association 7825 E. Gelding Dr., Suite 104, Scottsdale, AZ 85260

Copyright  $\bigcirc$  1998 by VMEbus International Trade Association All rights reserved.

No part of this publication may be reproduced in any form, in an electronic retrieval system or otherwise, without prior written permission of the publisher.

NOTE: The user's attention is called to the possibility that compliance with this standard may require use of one or more inventions covered by patent rights.

By publication of this standard, no position is taken with respect to the validity of such claims or of any patent rights in connection therewith. The patent holders have, however, filed a statement of willingness to grant a license under these rights on reasonable and nondiscriminatory terms and conditions to applicants desiring to obtain such a license for use of this standard. Details may be obtained from the publisher.

Printed in the United States of America - R1.0

ISBN 1-885731-12-4

## TABLE OF CONTENTS

| Forev                | vord                                                                                                                                                        | v      |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Chap<br>Intro<br>1.1 | duction to the VME64 Extensions standard<br>VME64 Extensions Objectives                                                                                     | 1      |

| 1.2<br>1.3           | 1.1.1 9U Boards, Backplanes and Subracks<br>Terminology<br>References                                                                                       | 2<br>2 |

| 1.4                  | 1.3.1 Connector Notes<br>Standard Terminology                                                                                                               |        |

|                      | ter 2<br>64x Compliance                                                                                                                                     |        |

| $2.1 \\ 2.2$         | Introduction<br>Requirements                                                                                                                                | 5<br>5 |

|                      | 2.2.1 6U VME64x Board's Minimum Features                                                                                                                    | .5     |

|                      | <ul><li>2.2.3 6U VME64x Backplane's Minimum Features</li><li>2.2.4 3U VME64x Backplane's Minimum Features</li></ul>                                         |        |

|                      | ter 3<br>1 & P2/J2 160 Pin Connectors                                                                                                                       | 7      |

| 3.1<br>3.2           | Introduction                                                                                                                                                | 7<br>7 |

|                      | 3.2.1 160 Pin Connector Placement<br>3.2.2 P1/J1 & P2/J2 Connectors, Rows z & d Pin Assignments                                                             | 7      |

|                      | <ul> <li>3.2.3 Geographical Address Pin Assignments</li> <li>3.2.4 +3.3V Power</li> <li>3.2.5 V1/V2 Auxiliary Power</li> </ul>                              | 10     |

|                      | 3.2.6 VPC Power and Additional +5V Power                                                                                                                    | 11     |

|                      | <ul><li>3.2.8 Board Power Dissipation</li><li>3.2.9 Backplane Termination Network using +3.3V Supply</li></ul>                                              | 12     |

|                      | <ul><li>3.2.10 Monolithic Backplanes</li><li>3.2.11 Geographical Address Implementation</li><li>3.2.12 Connector Pin Tail Lengths</li></ul>                 | 13     |

|                      | <ul><li>3.2.12 Connector Fin Tail Lengths</li><li>3.2.13 Labels on 96-pin Plug Connectors</li><li>3.2.14 Backplane Connectors with Keying Devices</li></ul> | 14     |

|                      | ter 4<br>0 Connector Area and VME64x Backplane Dimensions                                                                                                   |        |

| 4.1<br>4.2           | Introduction                                                                                                                                                | 17     |

|                      | 4.2.1 Connector Selection                                                                                                                                   | 18     |

|                      | <ul> <li>4.2.3 P0/J0 Pin Definitions</li> <li>4.2.4 P0/J0 Connector Mounting</li> <li>4.2.5 Pin Current Ratings</li> </ul>                                  | 19     |

|                      | <ul> <li>4.2.5 Fin Current Ratings</li> <li>4.2.6 Backplane P0/J0 Keying</li></ul>                                                                          | 20     |

| Chap                 | ter 5<br>Front Panels and Subracks                                                                                                                          | 23     |

| 5.1<br>5.2           | Introduction                                                                                                                                                | 23     |

|                      | 5.2.1 EMC Front Panels and Subracks                                                                                                                         |        |

|              | <ul><li>5.2.2 Solder Side Covers</li><li>5.2.3 Front Panel Label Areas</li></ul> |     |

|--------------|----------------------------------------------------------------------------------|-----|

| Char         | iter 6                                                                           |     |

|              | tor/Extractor Handles                                                            |     |

| 6.1          | Introduction                                                                     |     |

| 6.2          | Requirements                                                                     | .25 |

|              | 6.2.1 Handles                                                                    |     |

|              | 6.2.2 Subracks                                                                   | .25 |

|              | oter 7                                                                           |     |

|              | ng and Alignment Pin                                                             |     |

| $7.1 \\ 7.2$ | Introduction                                                                     |     |

| 1.4          | 7.2.1 Subrack Keying                                                             |     |

|              | 7.2.2 Board Keying                                                               |     |

|              | 7.2.3 Keying Number Identification                                               |     |

|              | 7.2.4 User Defined and User Installed                                            |     |

|              | 7.2.5 Multifunctional Alignment Pin                                              | .28 |

|              | oter 8                                                                           |     |

|              | and Front Panel Safety Ground Protection                                         |     |

| 8.1<br>8.2   | Introduction                                                                     |     |

| 0.4          | 8.2.1 ESD Strips on VME64 Boards                                                 |     |

|              | 8.2.2 ESD Clips in Card Guides and Subracks                                      |     |

|              | 8.2.3 Solder Side Covers with ESD Protection                                     | .32 |

|              | 8.2.4 Front Panel Design for ESD Protection                                      |     |

|              | 8.2.5 Front Panel Safety Ground Protection                                       | .32 |

|              | nter 9                                                                           |     |

|              | I/O Transition Boards                                                            |     |

| 9.1<br>9.2   | Introduction                                                                     |     |

| 9.4          | 9.2.1 Mechanical Dimensions                                                      |     |

|              | 9.2.2 Mechanical Components                                                      |     |

|              | 9.2.3 Board Layout Orientation                                                   |     |

|              | 9.2.4 Slot Keying Codes                                                          |     |

|              | 9.2.5 Connector Pin Labeling                                                     |     |

|              | 9.2.6 Increase in Backplane Height<br>9.2.7 Power to Rear I/O Transition Board   |     |

|              |                                                                                  |     |

|              | ter 10                                                                           |     |

| Addi         | tions to CR/CSR Definition                                                       | .37 |

|              | Introduction<br>Requirements                                                     |     |

| 10.2         | 10.2.1 The Defined CR Area                                                       |     |

|              | 10.2.1.1 CR/CSR Space Specification ID                                           | .39 |

|              | 10.2.1.2 Module Characteristics Parameters                                       | .39 |

|              | 10.2.1.3 Interrupt Capabilities                                                  |     |

|              | 10.2.1.4 Address Space Relocation                                                |     |

|              | 10.2.1.4.1 Data Access Width ParameteRs (DAWPR) Definition                       |     |

|              | 10.2.1.4.2 AM Capabilities Parameters (AMCAPs)                                   | 42  |

|              | 10.2.1.4.4 Address Decoder Masks (ADEMs)                                         | .43 |

|              | 10.2.1.5 Master Addressing Capabilities                                          | .44 |

|              | 10.2.2 The Defined CSR Area                                                      | .45 |

|              | 10.2.2.1 Additions to the Bit Set and Bit Clear Registers                        |     |

|              | 10.2.2.2 Address Decoder compaRe (ADER) Registers                                |     |

|              | 10.2.3 The User CR Area                                                          | .40 |

| 10.2.4 The Configuration RAM (CRAM) Area4910.2.5 The User CSR Area5010.2.6 Board Serial Number51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 11       57         2eVME Protocol       57         11.1 Introduction       57         11.1 Introduction       57         11.1 2 Edge Handshakes       57         11.1.2 Address Phases       57         11.1.3 Remapping the LWORD* Line       57         11.1.4 Extended AM Codes       57         11.1.5 Address Modes       57         11.1.6 Known Length 2eVME Transfers       58         11.1.7 Slave Terminated 2eVME Transfers       58         11.1.8 Slave Suspended 2eVME Transfers       59         11.1.9 Slave Error States       59         11.1.1 2eBTO Bus Time Out Timer       59         11.2.1 Transceivers and Connectors       59         11.2.2 Extended AM Codes       60         11.2.3 Data Size       60         11.2.4 Protocols - General       60         11.2.5 Address Phase Protocol and Timing       61         11.2.6 Data Phase Protocol and Timing       62         11.2.7 2eBTO(x) Bus Time Out Timer       62 |

| Appendix A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Appendix B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Appendix C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Appendix D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Appendix E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

## List of Figures

| Figure 3-1  | Backplane Termination Network using +3.3V Power             | 15 |

|-------------|-------------------------------------------------------------|----|

| Figure 4-1  | P0 Connector Layout Position on VME64x Boards               | 20 |

| Figure 4-2  | J0 Connector Layout Position on VME64x Backplanes           | 21 |

| Figure 4-3  | VME64x Backplane Left and Right End Dimensions              | 22 |

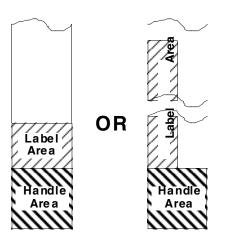

| Figure 5-1  | Front Panel Label Areas                                     | 24 |

| Figure 5-2  | Injector/Extractor Handle Label Area                        | 24 |

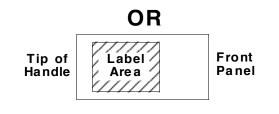

| Figure 7-1  | Keying Hole Positions and Associated Keying Codes           | 29 |

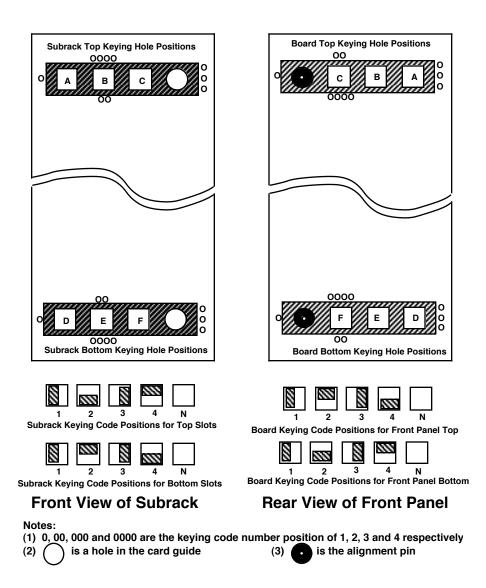

| Figure 9-1  | Front and Rear Board Orientation & Connector Pin Labeling   | 35 |

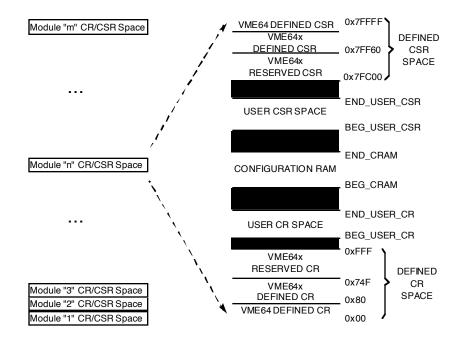

| Figure 10-1 | Structure of CR/CSR Space                                   |    |

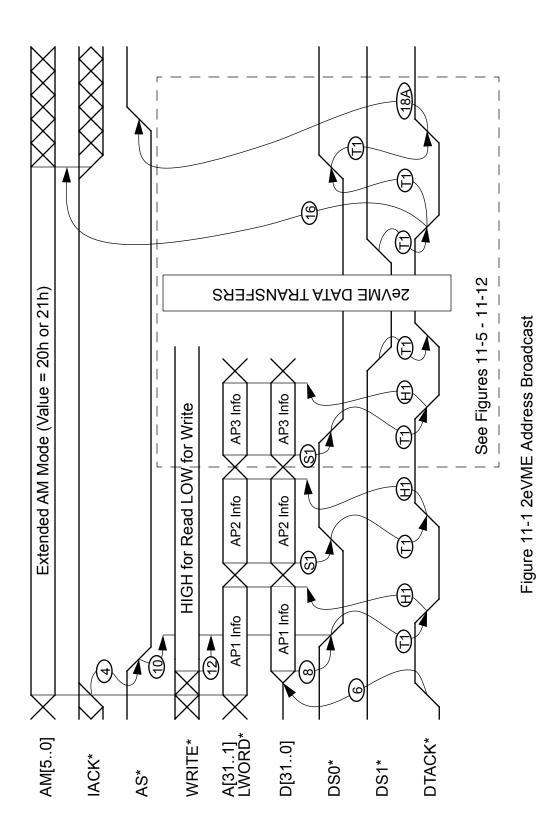

| Figure 11-1 | 2eVME Address Broadcast                                     | 65 |

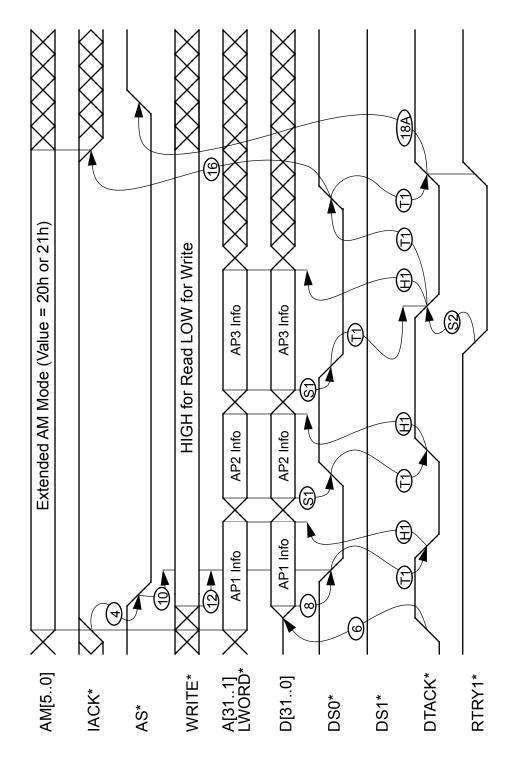

| Figure 11-2 | 2eVME Address Broadcast - Slave Suspend Response            | 66 |

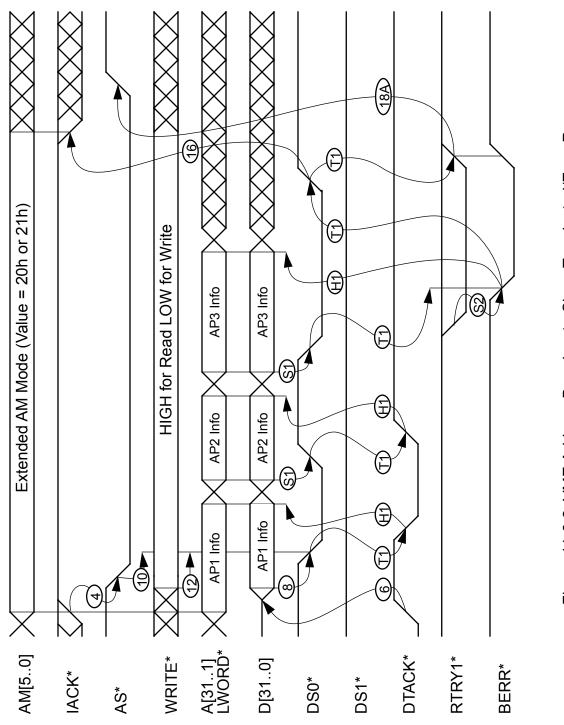

| Figure 11-3 | 2eVME Address Broadcast - Slave Stop/Error Response         | 67 |

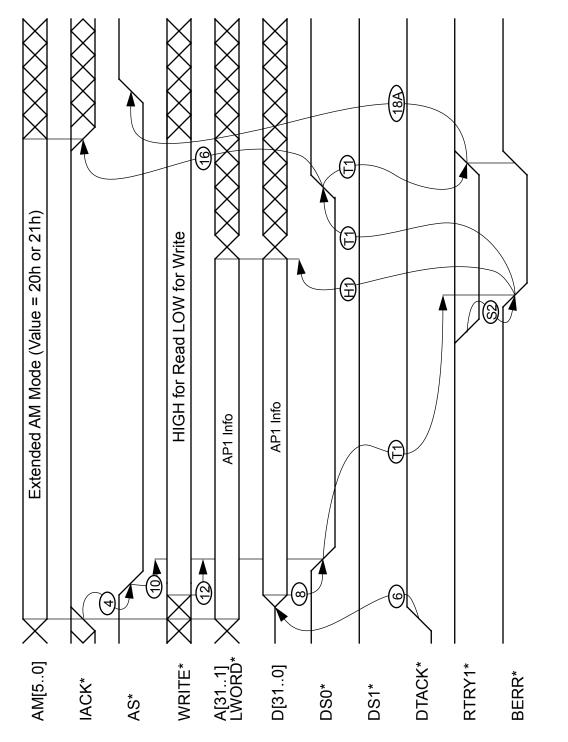

| Figure 11-4 | 2eVME Address Broadcast - Slave Suspend/Stop/Error Response |    |

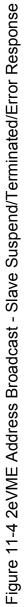

| Figure 11-5 | 2eVME Read Data Transfers - Master Termination              | 69 |

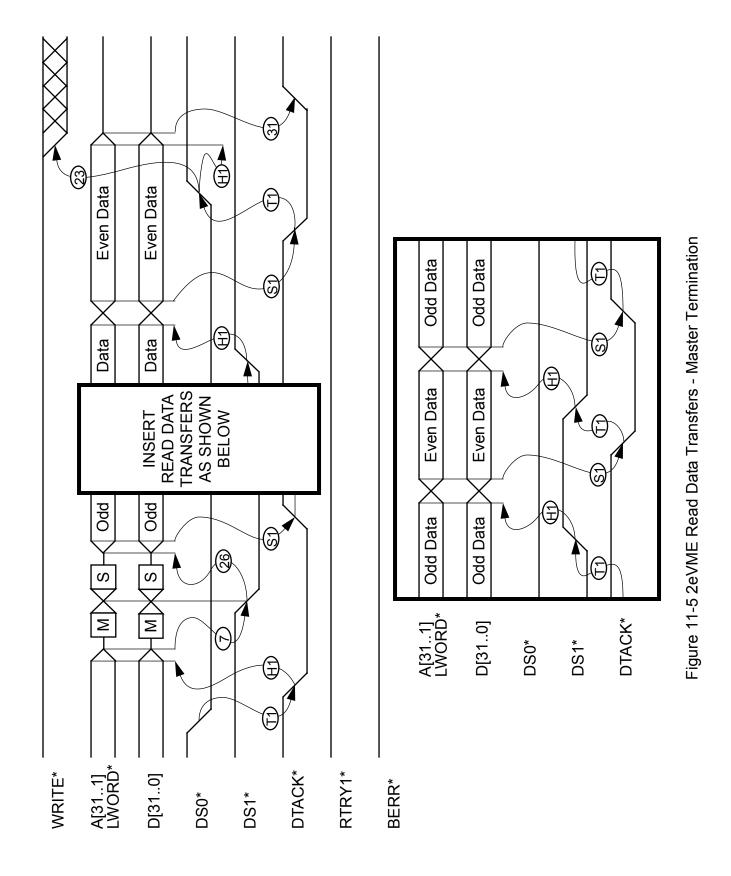

| Figure 11-6  | 2eVME Read Data Transfers - Slave Suspend                    | 70 |

|--------------|--------------------------------------------------------------|----|

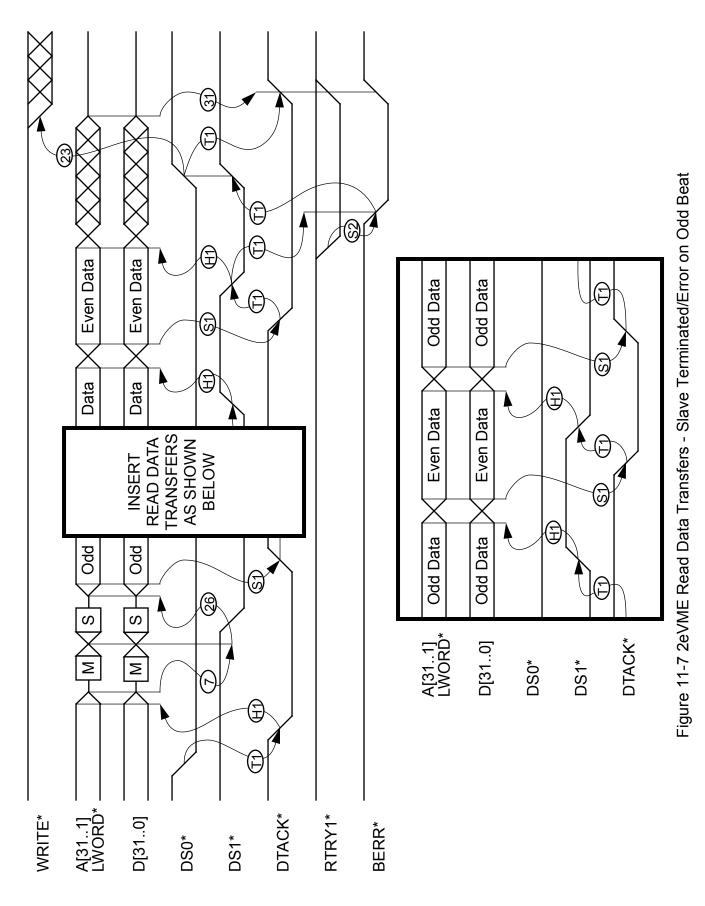

| Figure 11-7  | 2eVME Read Data Transfers - Slave Stop/Error on Odd Beat     | 71 |

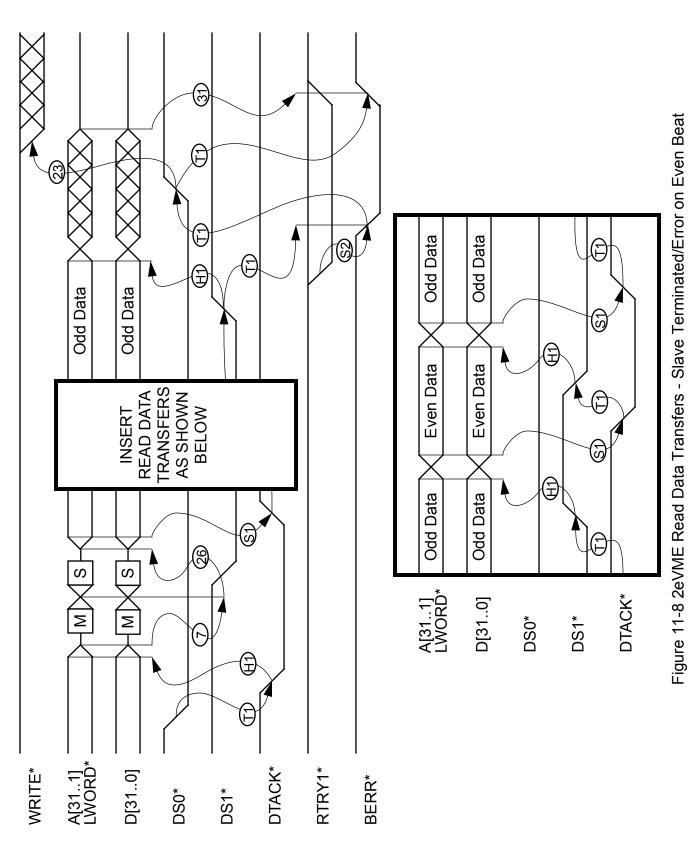

| Figure 11-8  | 2eVME Read Data Transfers - Slave Stop/Error on Even Beat .  | 72 |

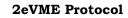

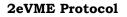

| Figure 11-9  | 2eVME Write Data Transfers - Master Termination              | 73 |

| Figure 11-10 | 2eVME Write Data Transfers - Slave Suspend                   | 74 |

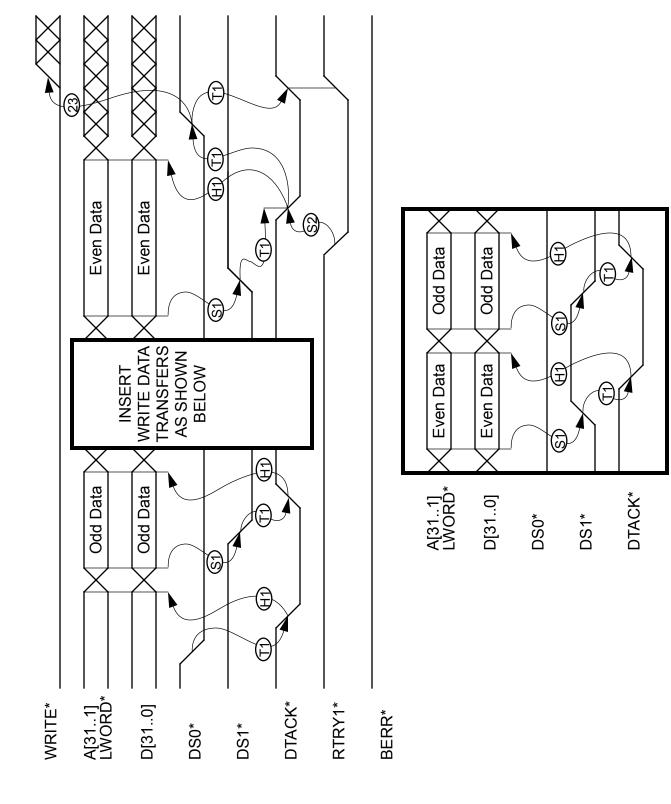

| Figure 11-11 | 2eVME Write Data Transfers - Slave Stop/Error on Odd Beat    | 75 |

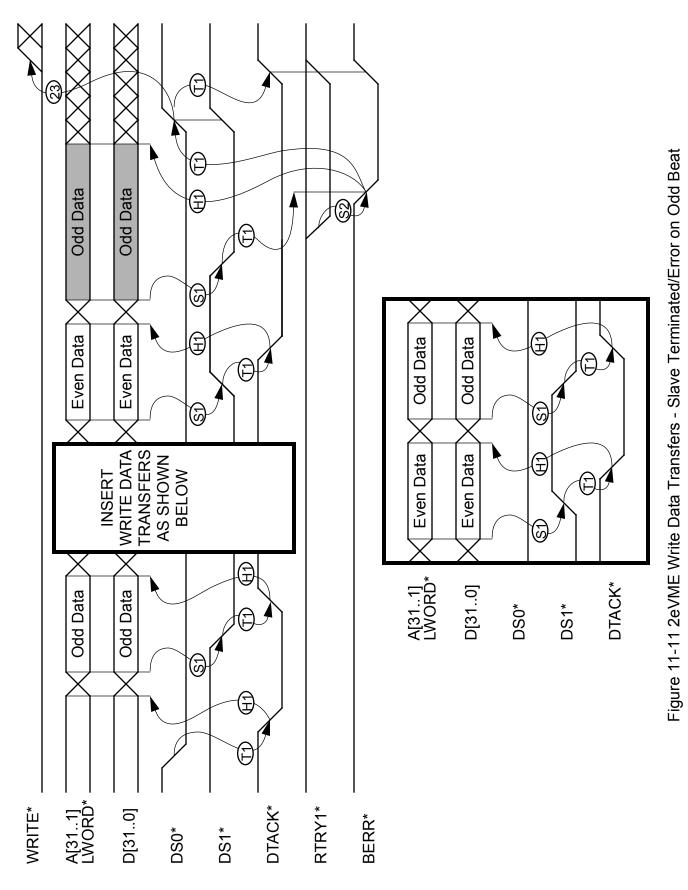

| Figure 11-12 | 2eVME Write Data Transfers - Slave Stop/Error on Even Beat . | 76 |

## List of Tables

| Table 3-1P1/J1 & P2/J2 Rows z & d Pin Assignments             |    |

|---------------------------------------------------------------|----|

| Table 3-2   Geographical Address Pin Assignments              | 10 |

| Table 4-1     P0/J0/RJ0/RP0 Connector Contact Labeling        | 19 |

| Table 10-1   Slave Characteristics Parameter                  |    |

| Table 10-2   Master Characteristics Parameter                 | 40 |

| Table 10-3 Data Access Width Parameter (DAWPR) Definitions    | 42 |

| Table 10-4 Address Decoder Mask (ADEM) Definitions            |    |

| Table 10-5    Address Relocation CR Examples                  |    |

| Table 10-6   Bit Set Register Assignment                      |    |

| Table 10-7   Bit Clear Register Assignment                    | 46 |

| Table 10-8 Address Decoder compaRe (ADER) Register Definition | 47 |

| Table 10-9 Address Relocation CR/CSR Examples                 | 48 |

| Table 10-10 CRAM_ACCESS_WIDTH Definition                      | 49 |

| Table 10-11 Serial Number Example                             | 51 |

| Table 10-12 Defined Configuration ROM Assignments             | 53 |

| Table 10-13 Defined Control/Status Register (CSR) Assignments |    |

| Table 11-1         Extended Address Modifier Line Definition  | 57 |

| Table 11-2    6U 2eVME Extended Address Modifier Codes        | 58 |

| Table 11-3    3U 2eVME Extended Address Modifier Codes        |    |

| Table 11-4   6U VME64x Signal Field Definition                | 63 |

| Table 11-5   3U VME64x Signal Field Definition                |    |

| Table 11-6   2eVME   Specific Timing Parameters               | 63 |

| Table 11-7   VME64 Timing Parameters                          | 64 |

#### Foreword

#### This Foreword is not part of ANSI/VITA 1.1-1997

VME became the industrial bus of choice in the 80's with hundreds of manufacturers supplying more than a thousand different boards to the world-wide market place. Thousands of customers utilized VME for a broad number of applications.

In the late 80's, the VME's draft standard was expanded for 64 bit data and address capability, which also doubled the throughput. Locks, Configuration ROM / Control & Status Registers (CR/CSR), rescinding DTACK\*, auto system control detection, auto slot ID, plus optional shielded DIN connectors were also added. These additional features effectively transformed VME from an 80's bus to a 90's bus, which allows VME to be used in even more demanding applications for the early 90's. This standard is commonly referred to as VME64.

In the summer of 1993 the VITA Standards Organization (VSO) agreed to publish the VME64 Standard. It was also agreed to use additional standards to add features as they are agreed upon by the VSO membership. This standard is a collection of additional features as agreed upon during 1994, 1995 and the first half of 1996. There will most likely be follow on standards with even more features.

Features added to VME64 in this standard encompass twenty major areas:

- 1) "z" and "d" pin rows to the P1/J1 and P2/J2 connectors for 160 pins in each connector.

- 2) An optional 2 mm hard metric 95 signal pin plus 19 or 38 ground pins P0/J0 connector for more user defined I/O through the backplane.

- 3) Supply voltages of +3.3 and auxiliary volts, plus more +5V power

- 4) 35 more signal ground returns between VME64x boards and VME64x backplanes for a total of 47 signal ground returns.

- 5) 46 more user defined I/O pins on the P2/J2 connector pair.

- 6) 14 bused spare pins and associated bused lines in the backplane, plus 2 unbused spare pins on the P1/J1 connector for future definition.

- 7) Pins allocated for a test and maintenance bus.

- 8) Slot geographical addressing.

- 9) Mechanical support for electromagnetic compatibility (EMC) control.

- 10) Mechanical support for electrostatic discharge (ESD) control.

- 11) Solder side covers with ESD protection.

- 12) An injection/extraction handle with a locking feature.

- 13) User installed board to slot keying

- 14) Alignment pin which supports solid keying, improved connector alignment, front panel ESD protection and EMC gasket alignment.

- 15) Front Panel Safety Ground.

- 16) Reserved area on the front panel for attachment of ID and/or bar code labels.

- 17) Rear I/O transition boards.

- 18) Added CR/CSR definition.

- 19) Supporting specifications for hot swap.

- 20) 2eVME: fast 2 edge protocol.

Some of these features are independent of one another. Others are tied close together, such as the usage of +3.3 V which requires the new 160 pin connector for the P1 connector on VME64x boards and the usage of the VME64x backplane. If the 160 pin connector is used on a VME64x board, the usage of 3.3 volt power, 48 volt power, hot swap control, serial bus, etc. are independent of one another.

Wayne Fischer, Force Computers, was chair of the VSO (VITA Standards Organization) task group that developed the draft for this standard. The following people participated in the ANSI canvass ballot.

Malcolm Airst, MITRE Corporation Harry Andreas, Raytheon Systems Company Tom Baillio, Mercury Computer Systems, Inc. Ed Barsotti, Fermi Nat'l. Accelerator Lab Joe Bedard, Hewlett-Packard Company Drew Berding, Arizona Digital Martin Blake, VERO Electronics James Botte, Nortel John Bratton, VERO Electronics Gorky Chin, VISTA Controls Corporation Louis Costrell, NIST Dick DeBock, Matrix Corporation Robert Downing, J. J. Dumont, Framatome Connectors France Darrell Ferris, Boeing Wayne Fischer, Force Computers Lou Francz, Dialogic Corporation Stephen Guentner, Systran Corporation Michael Harms, Stanford Linear Accelerator Center Mike Hasenfratz, Micro Memory, Inc. Frank Heine, Digital Equipment GmbH Roger Hinsdale, IBM Corporation Frank Hom, Electronic Solutions, Inc. Jim Koser, Berg Electronics, Inc. Tad Kubic, Dawn VME Products, Inc. Jing Kwok, Nexus Technology Andreas Lenkisch, Trenew Electronic GmbH Mike Macpherson, VISTA Controls Corporation Tim Marchant, Spectrum Signal Processing Patrick McHugh, LogicVision Robert McKee, MITRE Corporation Jonathan Morris, Tundra Semiconductor Corporation James Pangburn, Fermi Nat'l Accelerator Lab Chris Parkman, CERN Elwood Parsons, AMP Robert Patterson, AMP Inc David Robak, Harting Inc. of North America John Rynearson, VITA Keith Schuh, Fermi Lab Holly Sherfinski, Harting Inc. of North America Dick Somes, Digital Equipment Corporation Hermann Strass, Technology Consulting Mark Taylor, Westinghouse Electric Corporation Michael Thompson, Schroff, Inc. Frank Van Hooft, Spectrum Signal Processing Eike Waltz, Rittal Corporation Paul Weber, Synergy Microsystems, Inc.

## Introduction to the VME64 Extensions Standard

#### 1.1 VME64 Extension Objectives

This standard documents features that can be added to VME64 boards, backplanes and subracks defined in the VME64 Standard.

The following new features are defined for optional usage in VME64x based applications:

- Addition of z & d rows to P1/J1 and P2/J2 connectors - With associated pin assignments

- A 2 mm hard metric P0/J0 connector (area) between P1/J1 and P2/J2 connectors

With 95 user defined signal pins and 19 or 38 ground pins

- 35 more signal ground return pins in the P1/J1 and P2/J2 connectors

- +3.3 volt power

- Auxiliary power voltage

- 3 more +5V power pins via the 3 VPC power pins

- Slot geographical addressing

- 12 reserved bused signal lines, plus 2 unbused pins for future expansion

- 46 more user defined pins on the P2/J2 connector

- Pins allocated for a test and maintenance bus (T&Mbus)

- 3 mate first-break-last precharge voltage pins for hot swap applications

2 pins are on the P1/J1 connector and 1 pin on the P2/J2 connector

Can also be used for +5V power when board is locked into position

- Required for hot swap applications

- 3 mate first-break-last precharge ground pins for hot swap applications

2 pins are on the P1/J1 connector and 1 pin on the P2/J2 connector

Required for hot swap applications

- 2 reserved pins for individual slot power control for hot swap applications

- Front panel EMC protection

- ESD protection

- Solder side covers for hot swap and ESD protection

- Injector/Extractor handles with optional locking feature

- Board slot keying

- Multifunction alignment pin

- Front panel safety ground

- Reserved area on front panel for ID and bar code labels

- Rear I/O transition boards

- Added CR/CSR definition

- A 2eVME protocol that doubles the theoretical peak data transfer rate to 160 MB/sec

#### 1.1.1 VME64 Extensions and VME64x Usage

The phrase "VME64 Extension" has been shortened to VME64x, where "x" implies the "Extensions" word. In product data sheets, user manuals, advertising and other promotional literature, it is encouraged that only these two phrases be used when referencing this standard.

#### 1.1.2 9U Boards, Backplanes and Subracks

9U VME, VME64 and VME64x boards, backplanes and subracks will not be referenced in this standard. Another VSO standard, ANSI/VITA 1.3-1997, VME64x 9U x 400mm Format, specifically defines this capability.

#### 1.2 Terminology

See Appendix A for the new terminology specific to the added features described in this standard. Terminology described in the VME64 Standard is not repeated in Appendix A.

#### 1.3 References

The following publications are used in conjunction with this standard. When they are superseded by an approved revision, that revision must apply.

| ANSI/VITA 1-1994  | VME64 Standard, Approved April 10, 1995                                                                                                                     |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IEC 61076-4-113   | 2.54 mm 160 pin connectors complementary to IEC 603-2 Style C connectors                                                                                    |

| IEC 61076-4-101   | 2 mm Hard Metric Connector                                                                                                                                  |

| IEEE 1101.2-1992  | IEEE Standard for Mechanical Core Specifications for Conduction-Cooled Eurocards                                                                            |

| IEEE 1101.10-1996 | IEEE Standard for additional Mechanical Specification for<br>Microcomputers using the IEEE 1101.1 Equipment Practice                                        |

| IEEE 1101.11-1998 | IEEE Standard for Rear Plug-In Units for Microcomputers using the IEEE 1101.1 Equipment Practice, and the IEEE 1101.10 additional Mechanical Specifications |

| IEEE 1149.5-1995  | IEEE Standard Module Test and Maintenance Bus                                                                                                               |

| VITA 1.4          | VME64x Live Insertion Draft Standard                                                                                                                        |

| VITA 1.6          | Keying for Conduction Cooled VME64x Draft Standard                                                                                                          |

| VITA 2            | Enhanced Transceiver Logic Device Standard                                                                                                                  |

|                   |                                                                                                                                                             |

#### **1.3.1 Connector Notes**

The 160 pin connector defined in the IEC 61076-4-113 connector specification is an expanded 96 pin connector that is complementary to the IEC 603-2 Style C connector. Rows a, b & c are identical in form, fit and function to the 96 pin IEC 603-2 Style C connectors, used in original VME and VME64 applications. Rows z and d adds 64 pins to the outer shell for a total of 160 pins.

The 160 pin connectors are forward and backward compatible to the 96 pin connectors. Boards with 160 pin connectors will plug into backplanes using 96 pin connectors and boards with 96 pin connectors will plug into backplanes using 160 pin connectors.

IEC 61076-4-101 defines a family of 2 mm Hard Metric (HM) connectors. The P0/J0/RJ0/RP0 connectors defined in Chapter 3 use a Type B 25 position 2 mm connector variant with 19 positions. Each position provides 5 signal pins plus one or two ground pins.

#### 1.4 Standard Terminology

To avoid confusion and to make very clear what the requirements for compliance are, many of the paragraphs in this standard are labeled with keywords that indicate the type of information they contain. The keywords are listed below:

Rule Recommendation Suggestion Permission Observation

Any text not labeled with one of these keywords describes the VME64 structure or operation. It is written in either a descriptive or a narrative style. These keywords are used as follows:

#### Rule <chapter>.<number>:

Rules form the basic framework of this standard. They are sometimes expressed in text form and sometimes in the form of figures, tables or drawings. All rules shall be followed to ensure compatibility between board and backplane designs. All rules use the words "shall" or "shall not" to emphasize the importance of the rule. The words "shall" or "shall not" are reserved exclusively for stating rules in this standard and are not used for any other purpose.

#### **Recommendation** <chapter>.<number>:

Wherever a recommendation appears, designers would be wise to take the advice given. Doing otherwise might result in some awkward problems or poor performance. While the VME64x architecture has been designed to support high-performance systems, it is possible to design a system that complies with all the rules but has poor performance. In many cases a designer needs a certain level of experience in order to design boards that deliver top performance. Recommendations found in this standard are based on this kind of experience and are provided to designers to speed their traversal of the learning curve. All recommendations use the words "should" or "should not" to emphasize the importance of the recommendation. The words "should" or "should not" are reserved exclusively for stating permissions in this standard and are not used for any other purpose.

#### Suggestion <chapter>.<number>:

A suggestion contains advice which is helpful but not vital. The reader is encouraged to consider the advice before discarding it. Some decisions that need to be made in designing boards are difficult until experience has been gained. Suggestions are included to help a designer who has not yet gained this experience. Some suggestions have to do with designing boards that can be easily reconfigured for compatibility with other boards, or with designing the board to make the job of system debugging easier.

#### **Permission** <chapter>.<number>:

In some cases a rule does not specifically prohibit a certain design approach, but the reader might be left wondering whether that approach might violate the spirit of the rule or whether it might lead to some subtle problem. Permissions reassure the reader that a certain approach is acceptable and will cause no problems. All permissions use the word "may" to emphasize the importance of the permission. The lower-case word "may" is reserved exclusively for stating permissions in this standard and is not used for any other purpose.

#### **Observation** <chapter>.<number>:

Observations do not offer any specific advice. They usually follow naturally from what has just been discussed. They spell out the implications of certain rules and bring attention to things that might otherwise be overlooked. They also give the rationale behind certain rules so that the reader understands why the rule must be followed.

## VME64x Compliance

#### 2.1 Introduction

In order for VME64x boards and VME64x backplanes to be labeled as VME64x Compliant, they are to incorporate a minimum set of functional features. This chapter specifies that minimum set of features for 3U and 6U boards and backplanes.

Each of these features are described and documented in subsequent chapters within this standard.

#### 2.2 Requirements

#### Rule 2.1:

To claim compliance to this standard, a product shall also comply to all the appropriate rules in ANSI/VITA 1-1994 VME64 Standard.

#### Rule 2.2:

In the event of any conflicts between this standard and a referenced standard or specification, this standard shall take precedence.

#### 2.2.1 6U VME64x Board's Minimum Features

#### Rule 2.3:

In order to be labeled as a VME64x compliant board, the 6U board shall incorporate the following minimum functional features:

- Use the IEC 61076-4-113 160 pin connectors for both the P1 and P2 connectors

- Connect all assigned connector ground pins in rows *z*, *a*, *b*, and *c* to the board's ground plane (row d ground pins are optional)

#### **Observation 2.1:**

All the other features defined in this standard are optional.

#### 2.2.2 3U VME64x Board's Minimum Features

#### Rule 2.4:

In order to be labeled as a VME64x compliant board, the 3U board shall incorporate the following minimum functional features:

- Use the IEC 61076-4-113 160 pin connector for the P1 connector

- Connect all assigned connector ground pins in rows z, a, b, and c to the board's ground plane

#### **Observation 2.2:**

All the other features defined in this standard are optional.

#### 2.2.3 6U VME64x Backplane's Minimum Features

#### Rule 2.5:

In order to be labeled as a VME64x compliant backplane, the 6U backplane shall incorporate the following minimum functional features:

- Monolithic PCB

- Use the IEC 61076-4-113 160 pin connectors for both the J1 and J2 connectors, with properly defined pin tail lengths

- Connect all assigned connector ground pins in all rows to the backplane's ground plane

- Connect the geographical address pins as defined in this standard

- Route and terminate all defined VME64 and VME64x bused signal lines

- Provide power connection and distribution for +5V, +3.3V, +12V, -12V, +V1, +V2, -V1, -V2, VPC and +5V STDBY.

- If rear I/O is to be used on a backplane, rear connector(s) are designed per IEEE 1101.11 for support of rear I/O transition boards.

#### **Observation 2.3:**

All the other features defined in this standard are optional.

#### 2.2.4 3U VME64x Backplane's Minimum Features

#### Rule 2.6:

In order to be labeled as a VME64x compliant backplane, the 3U backplane shall incorporate the following minimum functional features:

- Use the IEC 61076-4-113 160 pin connector for the J1 connector, with properly defined pin tail lengths

- Connect all assigned connector ground pins in all rows to the backplane's ground plane

- Connect the geographical address pins as defined in this standard

- Route and terminate all defined VME64 and VME64x bused signal lines

- Provide power connection and distribution for +5V, +3.3V, +12V, -12V, +V1, +V2, -V1, -V2, VPC and +5V STDBY.

#### **Observation 2.4:**

All the other features defined in this standard are optional.

## P1/J1 & P2/J2 160 Pin Connectors

#### 3.1 Introduction

This chapter specifies the usage (beyond the VME64 Standard) of a 160 pin connector for both the P1/J1 and P2/J2 connector pairs. The 160 pin connector adds two 32 pin rows over the 96 pin (3 X 32) VME and VME64 connectors. The pin definitions for these added rows are defined in this chapter. This 160 pin connector pair is defined in the IEC 61076-4-113 Standard.

These added rows are called the "z" row and "d" row. The z row is adjacent to the a row and the d row is adjacent the c row. The five rows are labeled z, a, b, c and d. Mechanical placement of the 160 pin connectors on VME64x boards and on the VME64x backplanes is defined in IEEE 1101.10.

Each 160 pin connector provides 4 pins that mate-first-break-last (MFBL). The four MFBL pins are d1, d2, d31 and d32. On the P1/J1 connectors all 4 pins are used for hot swap and on the P2/J2 connector, only the lower 2 pins are used for hot swap. Three of these MFBL pins also available for additional +5V power.

#### 3.2 Requirements

#### 3.2.1 160 Pin Connector Placement

#### **Rule 3.1:**

VME64x boards shall use the IEC 61076-4-113 160 pin plug connectors for the P1 and P2 connector positions, with a minimum endurance level of 400 mating cycles, which is in accordance to IEC 61076-4-113 performance level 2.

#### Rule 3.2:

Placement of the P1 and P2 connectors on VME64x boards shall be per IEEE 1101.10.

#### Rule 3.3:

VME64x backplanes shall use the IEC 61076-4-113 160 pin receptacle connectors for the J1 and J2 connector positions, with a minimum endurance level of 400 mating cycles, which is in accordance to IEC 61076-4-113 performance level 2.

#### Rule 3.4:

Placement of the J1 and J2 connectors on VME64x backplanes shall be per  $\hbox{I\!E\!E\!E}$  1101.10.

#### Permission 3.1:

Selective loading only the signal and power pins in the P1 and P2 connectors may be used on VME64x boards.

#### Rule 3.5:

The ground pins shall always be loaded in the P1 and P2.

#### Rule 3.6:

All pins in the J1 and J2 connector shall always be loaded.

#### **Observation 3.1:**

In some applications, not all pins are needed (used) in the P1 and P2 connectors. Using selectively loaded connectors could provide a cost savings and will reduce insertion/withdrawal forces.

#### 3.2.2 P1/J1& P2/J2 Connectors, Rows z & d Pin Assignments

#### **Rule 3.7:**

The signal pin assignment of the P1/J1 and P2/J2 connector pairs, rows z and d shall be as defined in Table 3-1, P1/J1 and P2/J2 Rows z & d Pin Assignments. See Appendix B for definition of these signals.

| Position |  | P1/J1 and P2/J2 Rows 2 0 |         |  | P2/J2 |         |  |

|----------|--|--------------------------|---------|--|-------|---------|--|

| No.      |  | Row z                    | Row d   |  | Row z | Row d   |  |

| 1        |  | MPR                      | VPC (1) |  | UD    | UD (1)  |  |

|          |  |                          | · · /   |  |       |         |  |

| 2        |  | GND                      | GND (1) |  | GND   | UD (1)  |  |

| 3        |  | MCLK                     | +V1     |  | UD    | UD      |  |

| 4        |  | GND                      | +V2     |  | GND   | UD      |  |

| 5        |  | MSD                      | RsvU    |  | UD    | UD      |  |

| 6        |  | GND                      | -V1     |  | GND   | UD      |  |

| 7        |  | MMD                      | -V2     |  | UD    | UD      |  |

| 8        |  | GND                      | RsvU    |  | GND   | UD      |  |

| 9        |  | MCTL                     | GAP*    |  | UD    | UD      |  |

| 10       |  | GND                      | GA0*    |  | GND   | UD      |  |

| 11       |  | RESP*                    | GA1*    |  | UD    | UD      |  |

| 12       |  | GND                      | +3.3V   |  | GND   | UD      |  |

| 13       |  | RsvBus                   | GA2*    |  | UD    | UD      |  |

| 14       |  | GND                      | +3.3V   |  | GND   | UD      |  |

| 15       |  | RsvBus                   | GA3*    |  | UD    | UD      |  |

| 16       |  | GND                      | +3.3V   |  | GND   | UD      |  |

| 17       |  | RsvBus                   | GA4*    |  | UD    | UD      |  |

| 18       |  | GND                      | +3.3V   |  | GND   | UD      |  |

| 19       |  | RsvBus                   | RsvBus  |  | UD    | UD      |  |

| 20       |  | GND                      | +3.3V   |  | GND   | UD      |  |

| 21       |  | RsvBus                   | RsvBus  |  | UD    | UD      |  |

| 22       |  | GND                      | +3.3V   |  | GND   | UD      |  |

| 23       |  | RsvBus                   | RsvBus  |  | UD    | UD      |  |

| 24       |  | GND                      | +3.3V   |  | GND   | UD      |  |

| 25       |  | RsvBus                   | RsvBus  |  | UD    | UD      |  |

| 26       |  | GND                      | +3.3V   |  | GND   | UD      |  |

| 27       |  | RsvBus                   | LI/I*   |  | UD    | UD      |  |

| 28       |  | GND                      | +3.3V   |  | GND   | UD      |  |

| 29       |  | RsvBus                   | LI/O*   |  | UD    | UD      |  |

| 30       |  | GND                      | +3.3V   |  | GND   | UD      |  |

| 31       |  | RsvBus                   | GND (1) |  | UD    | GND (1) |  |

| 32       |  | GND                      | VPC (1) |  | GND   | VPC (1) |  |

Table 3-1 P1/J1 and P2/J2 Rows z & d Pin Assignments

Note: (1) These pins are MFBL (mate-first-break-last) pins

#### **Observation 3.2:**

Pins d1 and d2 of the P2 connector will mate before the other pins in rows z, a, b, c and d. Be aware that this could cause problems with user defined I/O signals when these pins mate before the other I/O pins during live insertion operations.

#### **Recommendation 3.1:**

Be aware that during live insertion operations, the VPC power could be applied first, therefore boards should be designed to tolerate the application of VPC before GND is connected. The same applies during live removal, where VPC could be the last contact to be removed.

#### **Observation 3.3:**

Specification of the +3.3V, +V (+V1 & +V2) & -V (-V1 & -V2) [Auxiliary] and VPC power are defined in Sections 3.2.4, 3.2.5 and 3.2.6 of this standard.

#### Rule 3.8:

The GND pins shall be connected to the VME64x board's signal ground plane and the VME64x backplane's signal ground plane.

#### Rule 3.9:

The UD, User Defined, pins shall be treated in the same fashion and have the same rules as the User Defined pins in the VME64 Standard.

#### Rule 3.10:

The RsvBus (reserved bused) pins shall not be used by VME64x boards and are reserved for future use.

#### Rule 3.11:

The 14 RsvBus pins, the 5 test and maintenance bus (MPR, MCLK, MSD, MMD & MCTL) pins and the RESP\* pin shall be bused and terminated on VME64x backplanes that implement a 160 pin connector for J1 in the same fashion and have the same rules as the other VME64 bused signals defined in the VME64 Standard.

#### Rule 3.12:

The LI/I\* (Live Insertion/Input) and LI/O\* (Live Insertion/Output) pins shall be reserved for specification by the VITA 1.4-199x VME64x Live Insertion Draft Standard.

#### **Observation 3.4:**

The LI/I\*, LI/O\* and RsvU pins are not bused but just feed through the backplane.

#### Rule 3.13:

The five test and maintenance bus signal lines (MPR, MCLK, MSD, MMD & MCTL) shall be reserved for specification by the IEEE 1149.5 MTM-Bus Standard.

#### Rule 3.14:

The ground (GND) return path on the backplane shall present a maximum peak to peak voltage differential of 50 mV across the backplane, measured between any connector pin making contact with the GND rail, under conditions of maximum current demand and all conditions of loading and noise expected for that system. Backplane termination networks are included in this rule. This applies for all frequencies, including DC.

#### Rule 3.15:

A voltage differential no greater than 50 mV shall be presented across the +5V, +3.3V, +12V and -12V power rails and 200 mV across the +V and -V power rails, when measured between any two connector pins making contact with the respective power rail, under conditions of maximum current demand and all conditions of loading and noise expected for that system. This applies for all frequencies, including DC.

#### **Observation 3.5:**

While VME64x boards (with 160 pin connectors) can physically be plugged into a VME64 backplane (with 96 pin connectors), the two outer rows of pins, z and d, will not be connected to anything.

#### **Recommendation 3.2:**

Given Observation 3.5, the user should determine from the vendor whether a specific VME64x compatible board can be configured to operate correctly in a VME64 backplane.

#### **Permission 3.2:**

Vendors may design VME64x boards that can only be used in VME64x backplanes.

#### 3.2.3 Geographical Address Pin Assignments

#### Rule 3.16:

The 6 geographical address pins (GA0\*, GA1\*, GA2\*, GA3\*, GA4\* and GAP\*) shall be tied to ground or left open (floating) on the backplane J1 connector as defined in Table 3-2, Geographical Address Pin Assignments.

| Slot | GAP*        | GA4* | GA3* | GA2* | GA1* | GA0* |

|------|-------------|------|------|------|------|------|

| No.  | Pin Pin Pin |      | Pin  | Pin  | Pin  |      |

| 1    | Open        | Open | Open | Open | Open | GND  |

| 2    | Open        | Open | Open | Open | GND  | Open |

| 3    | GND         | Open | Open | Open | GND  | GND  |

| 4    | Open        | Open | Open | GND  | Open | Open |

| 5    | GND         | Open | Open | GND  | Open | GND  |

| 6    | GND         | Open | Open | GND  | GND  | Open |

| 7    | Open        | Open | Open | GND  | GND  | GND  |

| 8    | Open        | Open | GND  | Open | Open | Open |

| 9    | GND         | Open | GND  | Open | Open | GND  |

| 10   | GND         | Open | GND  | Open | GND  | Open |

| 11   | Open        | Open | GND  | Open | GND  | GND  |

| 12   | GND         | Open | GND  | GND  | Open | Open |

| 13   | Open        | Open | GND  | GND  | Open | GND  |

| 14   | Open        | Open | GND  | GND  | GND  | Open |

| 15   | GND         | Open | GND  | GND  | GND  | GND  |

| 16   | Open        | GND  | Open | Open | Open | Open |

| 17   | GND         | GND  | Open | Open | Open | GND  |

| 18   | GND         | GND  | Open | Open | GND  | Open |

| 19   | Open        | GND  | Open | Open | GND  | GND  |

| 20   | GND         | GND  | Open | GND  | Open | Open |

| 21.  | Open        | GND  | Open | GND  | Open | GND  |

Table 3-2 Geographical Address Pin Assignments

#### **Observation 3.6:**

Boards which use the geographical address signals will most likely use a pull up resistor to Vcc. The device that samples the levels of the geographical address pins will read the inverted value of the slot number into which the board is plugged. When the board is plugged into a VME/VME64 backplane the slot number will be zero with a parity error (GAP\* open).

#### Rule 3.17:

The board shall limit the current through each geographical address pin to a maximum of 2 mA.

#### 3.2.4 +3.3V Power

#### Rule 3.18:

The +3.3V power supplied to each slot on the VME64x backplane shall remain within the limits of +3.25V to +3.45V, including regulation variation, noise and ripple frequencies to 20 MHz.

#### Rule 3.19:

The current drawn for +3.3V pins shall follow the maximum current draw per power pin as specified in the VME64 Standard, Figure 5-7, Current Rating For Power Pins.

#### **Observation 3.7:**

If the maximum board ambient temperature is  $60^{\circ}$  C, the maximum current that can be drawn per power pin in a multi-pin configuration is 1.25 Amp. With 10 +3.3V power pins on the P1/J1 connector pair, a nominal 41 watts of +3.3V power can be supplied to a VME64x board.

#### Rule 3.20:

+3.3V, +5V, +12V, -12V and Auxiliary power will ramp up and down independently of one another. Boards shall be designed to accommodate any combination of power up and down sequence without causing board failure.

#### 3.2.5 V1/V2 Auxiliary Power

#### Rule 3.21:

The V1/V2 auxiliary power supplied to each slot via the +V1, +V2, -V1 and -V2 power pins on the VME64x backplanes shall remain within the limits of 38V to 75V, including regulation variation, noise and ripple frequencies to 20 MHz.

#### Rule 3.22:

The current drawn for the +V1, +V2, -V1 and -V2 pins shall follow the maximum current draw per power pin specified in the VME64 Standard, Figure 5-7, Current Rating For Power Pins.

#### Rule 3.23:

Each board's power draw of the V1/V2 power shall be balanced between the +V1 plus +V2 and -V1 plus -V2 power pins, with no more than 1 mA of current going through the ground pins.

#### **Recommendation 3.3:**

The V1/V2 leakage current should be kept below 100 uA.

#### Rule 3.24:

The system auxiliary power supply of the V1/V2 power shall ensure that the +V1 and +V2 voltages are always above or equal to the ground voltage level and that the -V1 and -V2 voltages are always below or equal to the ground voltage level.

#### **Observation 3.8:**

If the +V1 and +V2 voltage rails are tied to ground and the +12V power is used, the nominal voltage between the +12V and the -V1 and -V2 power rails is 60 volts. With voltage tolerances, the 60 volt maximum is exceeded. Additional protection might be needed to comply with local and national regulatory agencies.

#### **Recommendation 3.4:**

System implementors and users should be aware that the United States Underwriters Laboratory (UL) rules that whenever any two power points within a system (black box) exceeds 60 V, it is considered unsafe for "human operation". The design of boards will allow for larger voltages between any combination of power rails. But, how a "VME64x System" is integrated is the responsibility of the system integrator, and should comply with all applicable laws and regulations with respect to safety and other computer requirements, including EMC.

#### **Observation 3.9:**

For some applications, dual V1/V2 power rails are required. It might be necessary to build backplanes that split the +V1 and +V2 into two power rails, and/or split the -V1 and -V2 into two power rails.

#### **Recommendation 3.5:**

The usage of single or dual V1/V2 supply and the decision whether the negative or the positive poles will be tied together, is up to the system configuration. Generic VME64x backplanes should provide individual connections for each of the +V1, +V2, -V1, -V2 power rails.

#### Rule 3.25:

Boards that use the dual V1/V2 power rails shall place diodes or equivalent on each of +V1 and +V2 power lines and on each of the -V1 and -V2 power lines. In event one of the V1/V2 power rails fails, the other power rail will supply the auxiliary power to the board.

#### 3.2.6 VPC Power and Additional +5V Power

VPC is collectively the three pre-charge voltage pins on the P1/J1 and P2/J2 connectors. These three pins mate a minimum of 1.5 mm before the other pins during live insertion. During live withdraw, these pins are the last to break contact. This feature is required to

support the hot swap capability defined in the VITA 1.4-199x VME64x Live Insertion Draft Standard.

#### Rule 3.26:

If VPC power is used, all three VPC power pins shall be used on 6U boards and both VPC power pins on 3U boards shall be used.

#### Rule 3.27:

The VPC voltage pins shall be connected directly to the backplane +5V power plane.

#### **Observation 3.10:**

Boards used for hot swap need to limit the peak current drawn through each of the VPC power pins during connector mating and disconnect operations. The current limit is defined by the VITA 1.4-199x VME64x Live Insertion Draft Standard.

#### **Permission 3.3:**

VPC power pins may be used for additional +5V power when fully plugged in and locked into position.

#### Rule 3.28:

If the VPC power pins are used for additional +5V power, the current drawn shall follow the maximum current draw per power pin as specified in the VME64 Standard, Figure 5-7, Current Rating For Power Pins.

#### **Observation 3.11:**

If VPC power is shorted to +5V power on a board, the board can't be used in hot swap applications.

#### 3.2.7 Reset and ACFail

#### Rule 3.29:

If +3.3V and/or Auxiliary power is used to power boards plugged into the backplane, the SYSRESET\* and ACFAIL\* signals operations levels shall include the proper functional levels of +3.3V and Auxiliary.

#### **Observation 3.12:**

Rule 3.29 implies that the SYSRESET\* and ACFAIL\* signal lines can not be released high (normal operation) until the monitored power voltages are in the proper operation levels. When any of the power signals goes outside the proper operation range, the SYSRESET\* signal line is asserted. The timing of these two signals remains the same as defined in the VME64 Standard.

#### 3.2.8 Board Power Dissipation

#### **Recommendation 3.6:**

Board suppliers should specify a board's maximum power dissipation and identify "hot spots" and any thermally sensitive components, which require higher cooling airflow than normal.

#### 3.2.9 Backplane Termination Network using +3.3V Supply

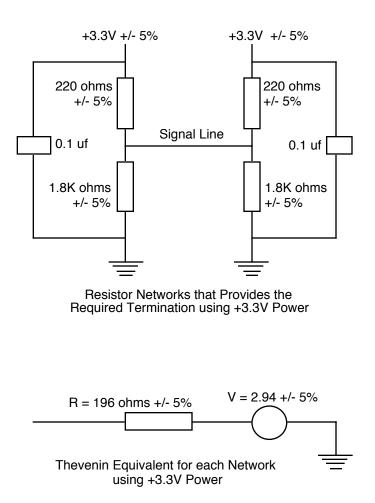

#### **Permission 3.4:**

The +3.3V supply voltage may be used for the backplane termination network's power.

#### Rule 3.30:

If the +3.3V supply voltage is used for the backplane termination network, the network shall be in compliance with the network shown in Figure 3-1 Backplane Termination Network using +3.3V Power.

#### **Recommendation 3.7:**

For VME64x backplanes that use +3.3V power for the termination network, a large warning label should be attached to the back side of the backplane stating that the termination network is supplied by the +3.3V power rails. "+3.3V power is required for proper VME64x system operation."

#### **Observation 3.13:**

The backplane voltage tolerance is better than required for the +3.3 V termination network.

#### **3.2.10** Monolithic Backplanes

#### Rule 3.31:

6U VME64x backplanes shall be constructed as a single (monolithic) printed circuit board.

#### **Observation 3.14:**

The main reason for Rule 3.31 is to provide solid voltage and ground planes on the backplane to minimize the noise and voltage differentials between VME64x boards and VME64x backplanes.

#### 3.2.11 Geographical Address Implementation

This section ties together the implementation of geographical addressing and CR/CSRs if both are implemented on a VME64x board.

Geographical addressing as defined in Section 2.2.3 is to be used by VME64x boards to automatically identify into which VME64x backplane slot it is plugged. Based on that information, software can automatically configure the boards for slot specific functionality. Initialization and configuration of the CR/CSRs is an extension of the capability.

The monarch is generally the first CPU board to gain access to the backplane and system right after power up to configure the system. The monarch might also be the CPU board which controls and manages the main system operation during normal operations.

#### Rule 3.32:

If a board implements both geographical addressing and CR/CSR capability, the BAR value shall be derived from the geographical address pins.

#### **Observation 3.15:**

The above rule will automatically place each board's CR/CSR address in the proper A24 address space. This will allow the system's monarch to search the CR/CSR address space and quickly determine which VME64x boards are plugged into the backplane and then configure the board.

#### **Recommendation 3.8:**

Boards implementing Rule 3.32 should parity check the geographical address. If bad parity is found, the local address should be set to decimal 30 (Ox1E) (the amnesia address).

#### **Permission 3.5:**

If bad geographical address parity is detected the board may not respond to CR/CSR accesses from the bus.

#### **Observation 3.16:**

It is up to the system designer to determine how to handle multiple occurrence of geographical parity errors, if multiple parity errors do occur.

#### Rule 3.33:

Monarchs that search the CR/CSRs space for presence of VME64x boards shall also look for boards at amnesia address 30 (Ox1E) and take the appropriate action if one is found at that address.

#### Permission 3.6:

VME64x boards that need to be backward compatible to original VME backplanes, may add some sense circuitry and 5 switches or 5 jumpers or some programmable logic. When the board senses that none of the GA\*[4..0] lines are tied to ground (board not plugged into a VME64x backplane), it will use the state of the 5 switches or 5 jumpers or programmable logic values for the geographical address value.

#### **Observation 3.17:**

The BAR bits 7 to 3 defined in the CR/CSR regions, correspond to A[23..19] in the CR/CSR space. See Table 2-31 and Section 2.3.12 in the VME64 Standard for more explanation.

#### **3.2.12** Connector Tail Lengths

#### **Recommendation 3.9:**

All backplane J1 and J2 connector tail pins that are connected to bus signal lines should be of the short length, 5 mm or less.

#### Rule 3.34:

If backplane application is intended to support rear I/O transition boards, then the J2 B row of power and ground pins shall be 17 mm in length.

#### **Observation 3.18:**

Recommendation 3.9 provides protection of the electrical properties of all bused signal lines on the backplane.

#### Rule 3.35:

When straight through I/O is used, a shroud over the rear long tail pins shall be used that meets the mechanical dimensions defined in IEEE P1101.11.

#### 3.2.13 Labels on 96-pin Plug Connectors

#### Rule 3.36:

All VME64 and VME64x boards that utilize the 96-pin plug connector shall not place labels or any other markings on the outer shroud.

#### **Observation 3.19:**

When 96-pin plug connectors are plugged in to a 160-pin receptacle connector, the two outer contact rows contact directly on the outer shroud. Any added material will cause the board's insertion forces to be higher as well as will rub off the labels or any other marking material.

#### 3.2.14 Backplane Connectors with Keying Devices

#### **Observation 3.20:**

Some VME boards and backplanes use 96-pin connectors with a built in keying device. A VME64x board with a 160-pin connector cannot be plugged into such a backplane. The outer rows of the 160-pin connector will be blocked by the keying device, preventing the two connectors from mating.

Figure 3-1 Backplane Termination Network using +3.3V Power

## PO/JO Connector Area and VME64x Backplane End Dimensions

#### 4.1 Introduction

At times manufacturers and users of VME64x boards have a need for additional and sometimes specialized I/O through the backplane. This chapter specifies the requirements and provides observations for implementation of user defined I/O between the P1/J1 and P2/J2 connectors.

This area is commonly called the PO/JO connector area, even though four connectors are involved: a connector on the front VME64x board (PO), a connector on the front of the backplane (JO), a connector shroud on the rear of the backplane (RJO) and a connector on the rear board (RPO) or the end of cable which plugs into the rear connector. This is sometimes written as: PO/JO/RJO/RPO, where the "R" means rear. (The rear connector shroud goes over the long tail pins and provides the necessary alignment and other mechanical support for normal connector mating.)

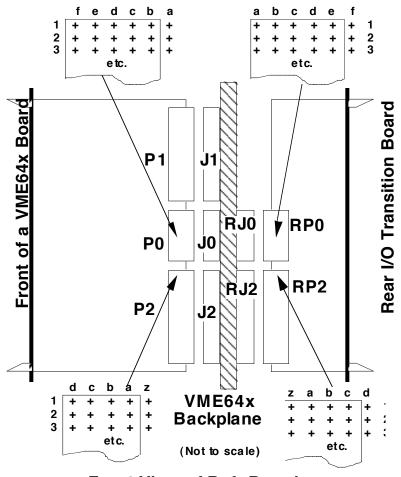

See Chapter 9 for the definition of rear I/O transition boards and for mechanical alignment with the backplane. See Figure 9-1 for a pictorial of the connector placements on VME64x boards, VME64x backplanes and rear I/O transition boards.

Due to usage of the J0, 2 mm connector, VME64x backplane's left and right end mechanical dimensions are shifted left, to accommodate the connector's added width and position. Section 4.2.7 defines VME64x backplane's left and right end dimension.

#### 4.2 Requirements

#### **Permission 4.1:**

Additional user defined I/O connector space may be obtained if the mechanical member between J1 and J2 connector pairs on VME backplanes, shown in Figure 7-18 of the VME64 Standard, is removed.

#### Rule 4.1:

Whenever a structural member is not used between the J1 and J2 connectors on VME64x backplanes, the VME64x backplane shall maintain sufficient rigidity to meet the mechanical requirements specified in IEEE 1101.1.

#### **Observation 4.1:**

VME64x boards using I/O connectors between P1 and P2 could conflict with VME/VME64 backplanes that have a structural member between J1 and J2 connectors.

#### 4.2.1 Connector Selection

#### **Rule 4.2:**

For generic use the 19 position, Type B, 2 mm hard metric, IEC 61076-4-101 connector family shall be used. The connectors shall be rated Performance Level 2 or better with a minimum of 250 insertion withdrawal cycles.

#### Rule 4.3:

For generic uses, the 19 position, Type B, 2 mm hard metric IEC 61076-4-101 free board connector shall be used on VME64x boards.

#### Rule 4.4:

For generic uses, the 19 position, Type B, 2 mm hard metric IEC 61076-4-101 fixed board connector shall be used on the VME64x backplanes. On the front side, rows z and f shall be length 3 (11.2 mm) and rows a through e shall be length 1 (8.2 mm). On the rear side, the pin tail lengths shall be 16 mm when straight through I/O is used, or less than 5.0 mm when a sub-bus is used.

#### Rule 4.5:

When straight through I/O is used, a shroud over the rear long tail pins shall be used that meets the mechanical dimensions defined in IEEE P1101.11.

#### Rule 4.6:

Where the 2 mm hard metric IEC 61076-4-101 connector is used, the z and f row pins on the backplane's fixed board connector shall be connected to the backplane's ground plane as defined in Table 4-1, PO/J0 Connector Pin Labeling.

#### Rule 4.7:

The z row shield on the free board P0 and RP0 connectors shall only be used if it does not protrude through the board's interboard separation plane, as defined in  $\mathbb{E}\mathbb{E}\mathbb{E}$  1101.1.

#### **Observation 4.2:**

Some of the 2 mm hard metric connector's z shields protrude into the interboard separation plane, and therefore can not be used.

#### **Observation 4.3:**

The two outer rows of contacts are connected to ground on the backplane. When only the f row shield is used on the free board connector, 19 ground contacts are supplied to the board. The use of both the f and z row shields provide a total of 38 ground contacts.

#### 4.2.2 Custom Connectors

#### Permission 4.2:

Custom I/O connectors such as coaxial cable or fiber may also be used on VME64x boards and VME64x backplanes which require specialized custom I/O in the P0/J0 connector area.

#### **Observation 4.4:**

VME64x backplanes with custom I/O connectors will not be compatible with VME64x boards containing a PO connector per Rule 4.2.

#### **Recommendation 4.1:**

The keying scheme defined in this standard should be used for boards and backplane slots that have custom I/O connectors.

#### **Recommendation 4.2:**

For applications that are 1101.2 based, the VITA 1.6-199x Keying for Conduction Cooled VME draft standard should be used.

#### Rule 4.8:

Any custom connector installed on the backplane in the J0 connector area shall allow the front board's rear edge to be installed (come to rest) within 12.5mm of the backplane surface.

#### **Observation 4.5:**

A connector with a height of greater than 12.5mm will protrude over the rear edge of a VME64x board when fully inserted into a slot. This would prevent generic boards, that do not have a mating P0 connector, from being inserted into that slot.

#### 4.2.3 PO/JO Pin Definitions

#### Rule 4.9:

The row and column labeling of the contacts in the PO/JO/RJO/RPO connector shall be as shown in Table 4-1, PO/JO/RJO/RPO Connector Contact Labeling.

| Pos. | Row f | Row e | Row d | Row c | Rows<br>b | Row a | Row z |

|------|-------|-------|-------|-------|-----------|-------|-------|

| 1    | OND   | ID    | ID    |       | -         | IID   | OND   |

| 1    | GND   | UD    | UD    | UD    | UD        | UD    | GND   |

| 2    | GND   | UD    | UD    | UD    | UD        | UD    | GND   |

| 3    | GND   | UD    | UD    | UD    | UD        | UD    | GND   |

| 4    | GND   | UD    | UD    | UD    | UD        | UD    | GND   |

| 5    | GND   | UD    | UD    | UD    | UD        | UD    | GND   |

| 6    | GND   | UD    | UD    | UD    | UD        | UD    | GND   |

| 7    | GND   | UD    | UD    | UD    | UD        | UD    | GND   |

| 8    | GND   | UD    | UD    | UD    | UD        | UD    | GND   |

| 9    | GND   | UD    | UD    | UD    | UD        | UD    | GND   |

| 10   | GND   | UD    | UD    | UD    | UD        | UD    | GND   |

| 11   | GND   | UD    | UD    | UD    | UD        | UD    | GND   |

| 12   | GND   | UD    | UD    | UD    | UD        | UD    | GND   |

| 13   | GND   | UD    | UD    | UD    | UD        | UD    | GND   |

| 14   | GND   | UD    | UD    | UD    | UD        | UD    | GND   |

| 15   | GND   | UD    | UD    | UD    | UD        | UD    | GND   |

| 16   | GND   | UD    | UD    | UD    | UD        | UD    | GND   |

| 17   | GND   | UD    | UD    | UD    | UD        | UD    | GND   |

| 18   | GND   | UD    | UD    | UD    | UD        | UD    | GND   |

| 19   | GND   | UD    | UD    | UD    | UD        | UD    | GND   |

Table 4-1 PO/JO/RJO/RPO Connector Contact Labeling

#### **Observation 4.6:**

The J0/RJ0 connectors have seven physical rows of contacts, with the z and f contact rows connected to the backplane's ground plane. On the VME64x board, there is no z row of contact holes Depending on the connector design, the P0 and RP0 connector ground contacts in the z and f row of the connector (which is on the connector shroud) will alternately connect to the board's f row of ground contacts.

#### **Observation 4.7:**

Connector layout and position numbering method is the same as the P1/J1 and P2/J2 connectors. Position 1 is near P1/J1's position 32 and position 19 is near P2/J2's position 1.

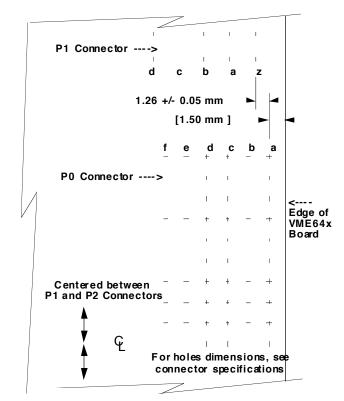

#### 4.2.4 PO/JO Connector Mounting

#### Rule 4.10:

Mounting of the 19 position, 5+1 row, Type B, 2 mm hard metric IEC 61076-4-101 free board connector on VME64x boards shall be as shown in Figure 4-1, when implemented

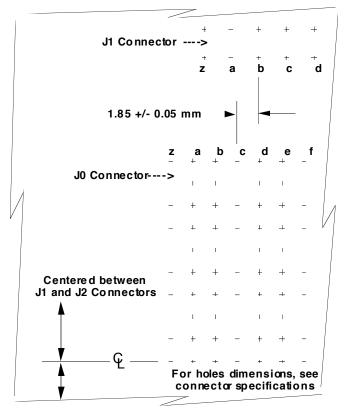

#### Rule 4.11:

Mounting of the 19 position, 5+2 row, Type B, 2 mm hard metric IEC 61076-4-101 fixed board connector on VME64x backplanes shall be as shown in Figure 4-2, when implemented.

#### 4.2.5 Pin Current Ratings

#### Rule 4.12:

The maximum current load per contact shall be in compliance to the IEC 61076-4-101.

#### **Observation 4.8:**

When the ANSI/VITA 1.1, VME64x standard was approved, the maximum current load per contact was defined to be 2.0 amp at  $70^{\circ}$  C when an alternate chess pattern of

contacts are used for power. When adjacent contacts are grouped together for power, the maximum current per contact is 1.0 amp at  $70^{\circ}$  C. The current rating of the shield contacts in rows z & f is 1.5 amp at the same temperature. For power ratings at other temperatures, see IEC 61076-4-101.

#### Rule 4.13:

The shield contacts are connected to logic ground on the backplane and boards. It is not connected to frame ground. Although the shield contacts will provide a ground return path the current carrying capacity of the pins shall not be used in calculating the overall ground current carrying capacity.

Figure 4-1 PO Connector Layout Position on VME64x Boards

(component side - top view)

#### 4.2.6 Backplane PO/JO Keying

In some applications a slot board to backplane keying is required. In particular, IEEE 1101.2 type applications do not use the front panel, but do require slot keying.

#### **Recommendation 4.3:**

For applications that need a slot board to backplane keying capability, the keys defined in VITA 1.6-199x Keying for Conduction Cooled VME should be used.

Figure 4-2 J0 Connector Layout Position on VME64x Backplanes (front view)

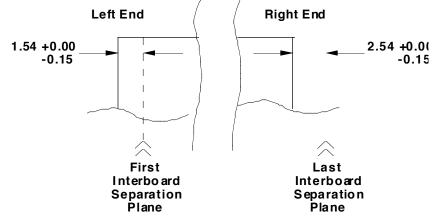

#### 4.2.7 VME64x Backplane End Dimensions

Mounting of the J0 2 mm connector on VME64x backplanes causes the backplane to be shifted to the left on both the left and right ends, over VME/VME64 backplanes. Only the two end dimensions are affected. All the other backplane dimensions remain the same as defined in the VME64 Standard.

When two VME64x backplanes of less than 21 slots are mounted next to one another in the same subrack, the gap between the two backplanes is designed to be 1 mm. In the VME64 Standard, this dimension is defined as 1.44 mm. Depending on the specific application needs, backplanes can be made wider. The incremental width needs to be consistent such that when backplanes are mounted next to one another or mounted next to other hardware, such as disk drive or power supplies, the gap always remains the same, regardless of the backplane width and number of slots used.

#### Rule 4.14:

The left and right end dimensions of minimum width VME64x backplanes shall be as shown in Figure 4-3.

#### Rule 4.15:

If VME64x backplanes need to be made wider, the incremental end dimensions for both left and right ends shall be in 5.08 mm (1 HP) increments.

#### **Permission 4.3:**

For subrack airflow management purposes, the right end of 21 slot sized VME64x backplanes may extend over the last interboard separation plane by 1.54 + 0.00 - 0.15 mm.

#### Rule 4.16:

Half shears shall not exceed 1.00 mm in height when used in VME64x applications.

#### **Observation 4.9:**

Note that half shears are commonly used on side (end) plates of subracks to prevent rotation and ensure accurate alignment of subrack horizontal members.

#### Rule 4.17:

Some side (end) plates that utilize half shears for positioning of horizontal members, shall not place half shears in the area of the backplane ends, as shown in Figure 4-3.

#### **Observation 4.10:**

All the other backplane dimensions and tolerances remain the same as defined in the VME64 Standard.

Figure 4-3 VME64x Backplane Left and Right End Dimensions

(front view)

#### **Observation 4.11:**