# **XFEL Timing System**

# **Status 7.2008**

Attila Hidvégi Patrick Geßler Kay Rehlich

Kay Rehlich 10.7.2008

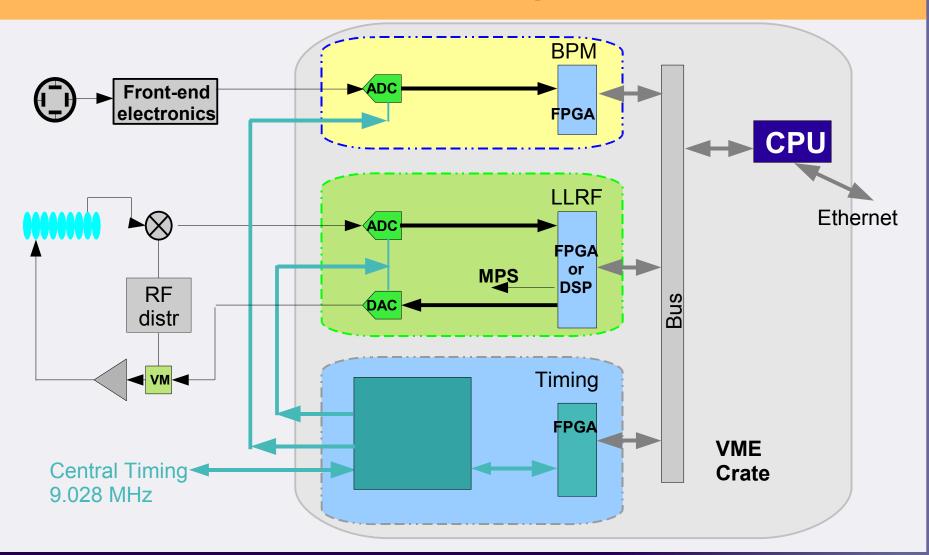

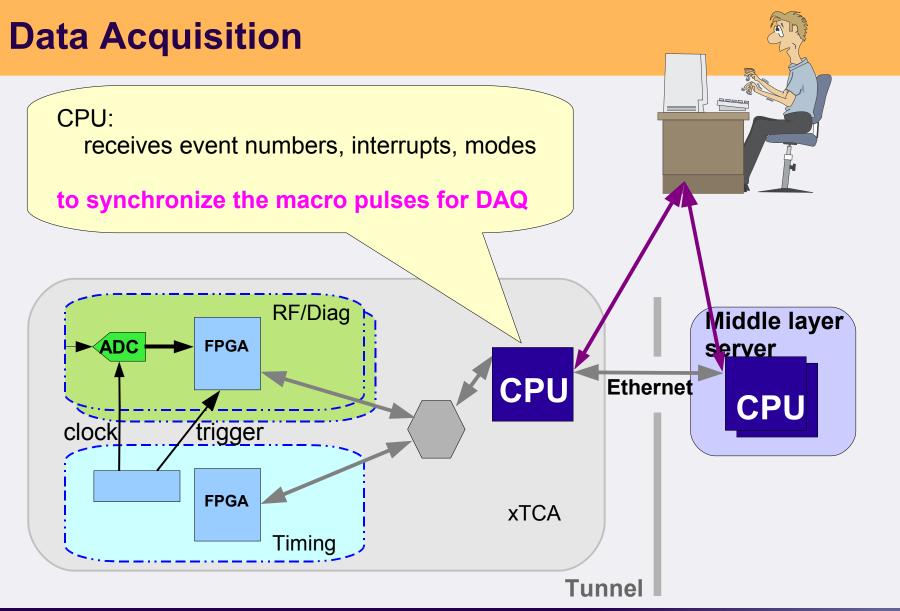

### **The Front-end: FLASH Example**

A

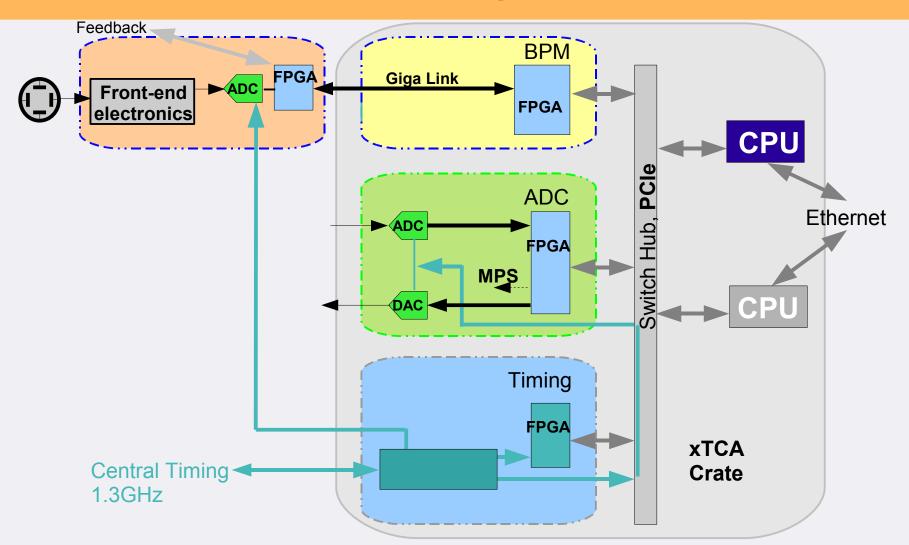

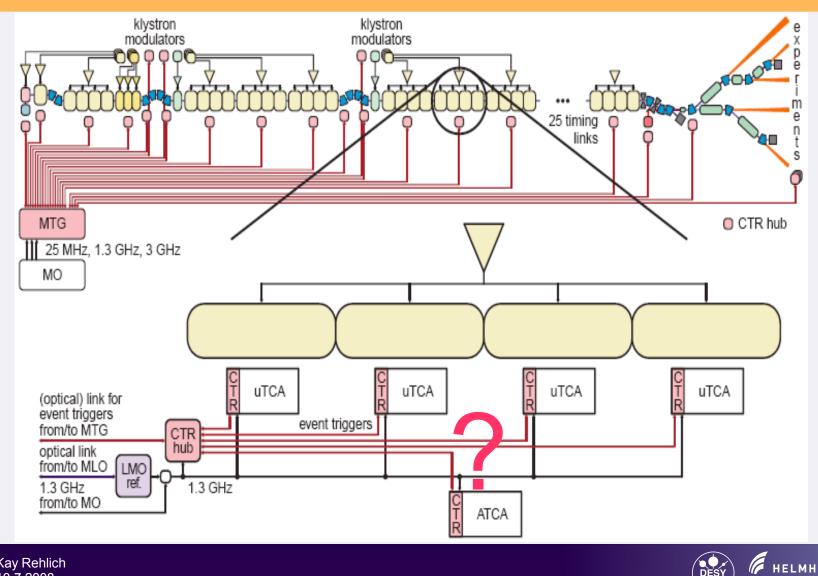

### **The Front-end: XFEL Examples**

Kay Rehlich

10.7.2008

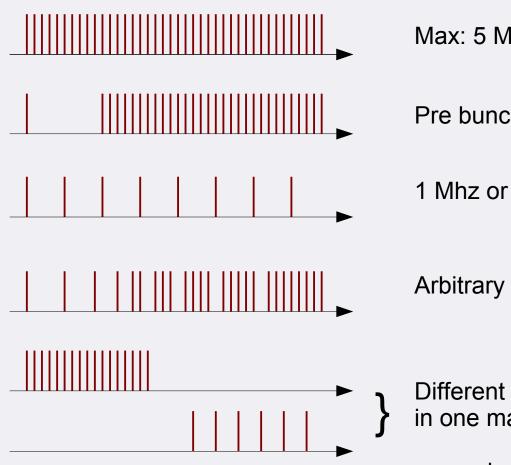

## **Possible Bunch Patterns**

Kay Rehlich

10.7.2008

Max: 5 Mhz, 3000 bunches

Pre bunch

1 Mhz or lower frequencies

Arbitrary patterns

Different patterns @ different beamlines in one macro pulse

or varying patterns from shot to shot

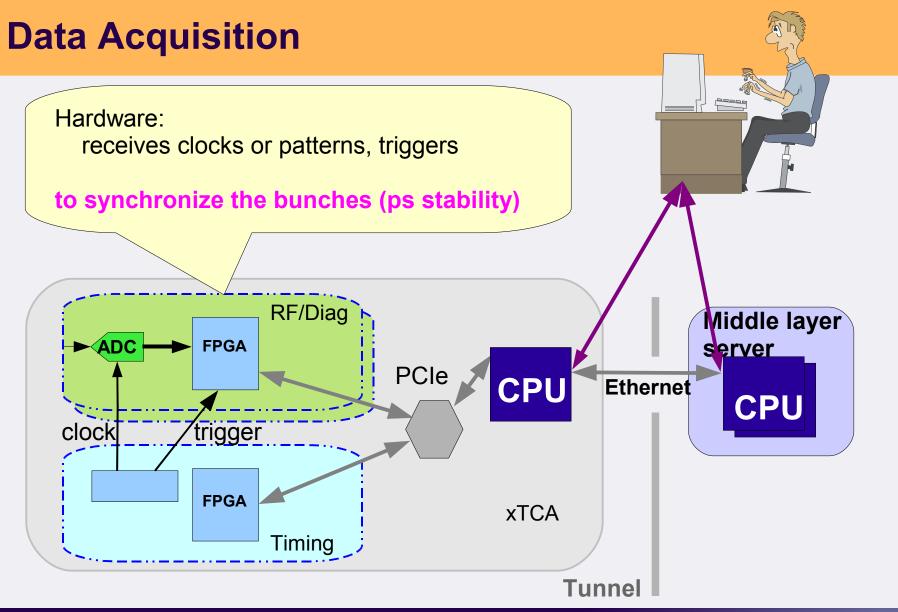

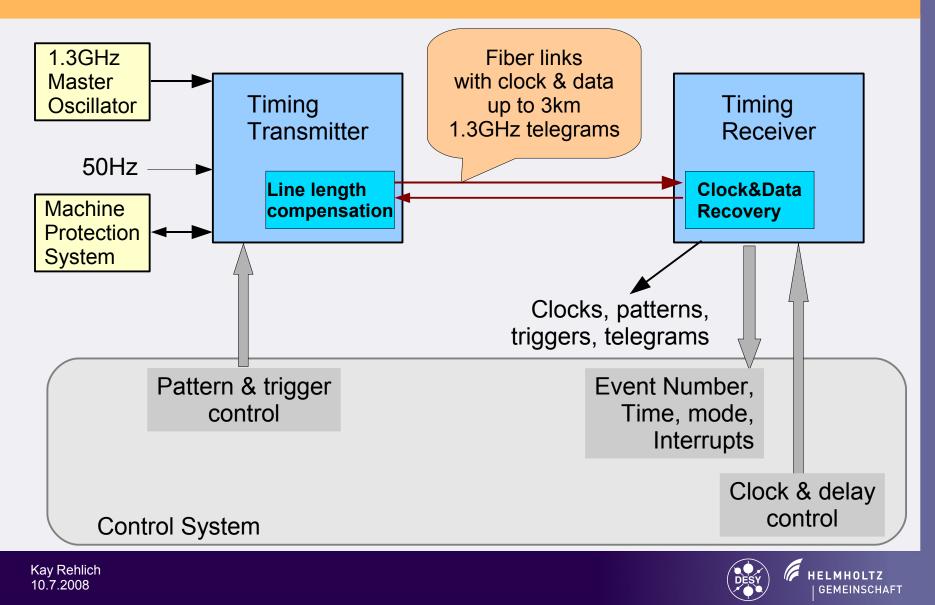

# **Timing System Blocks**

# **Timing System Requirements**

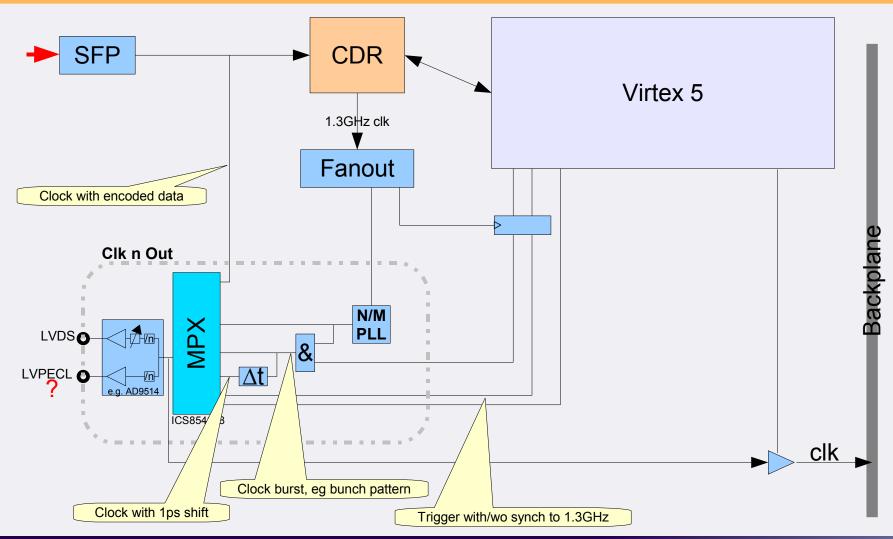

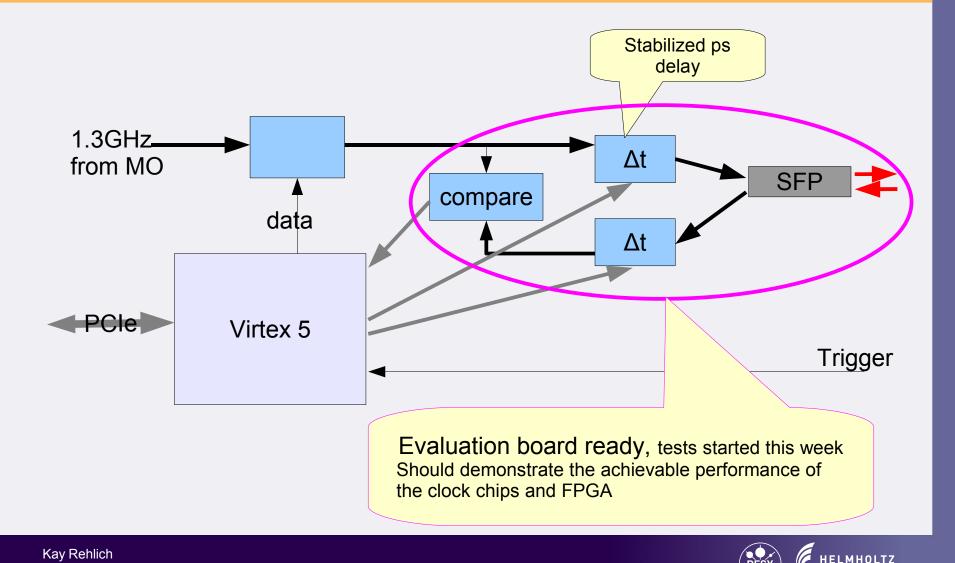

#### 1.3GHz telegrams

- With clock recovery, few ps jitter

- Events and data for triggers, event number, modes, bunch pattern, (bunch charge?), ...

- Sender compensates cable length, drifts and measures time delay from sender to receiver

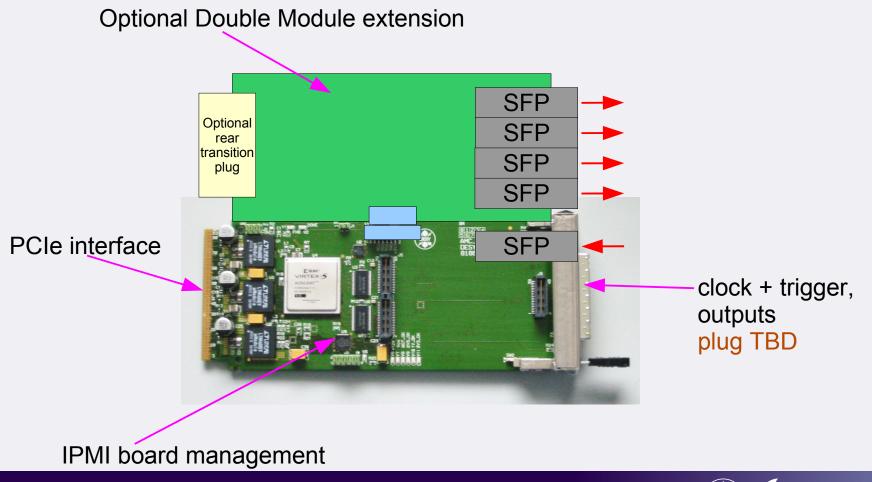

### Timing receiver outputs (hardware)

- Raw telegrams

- Clock (and gated clocks) on front and backplane

- triggers

Kay Rehlich 10.7.2008

- Level (LVDS, LVPCL,..) to be defined

- Connectors to be defined (e.g. infiniband)

# **Timing Distribution**

HELMHOLTZ

**GEMEINSCHAFT**

## **Possible AMC – Timing Receiver Module**

# **Preliminary: output block**

Kay Rehlich

10.7.2008

A

GEMEINSCHAFT

### **Preliminary: sender block**

10.7.2008

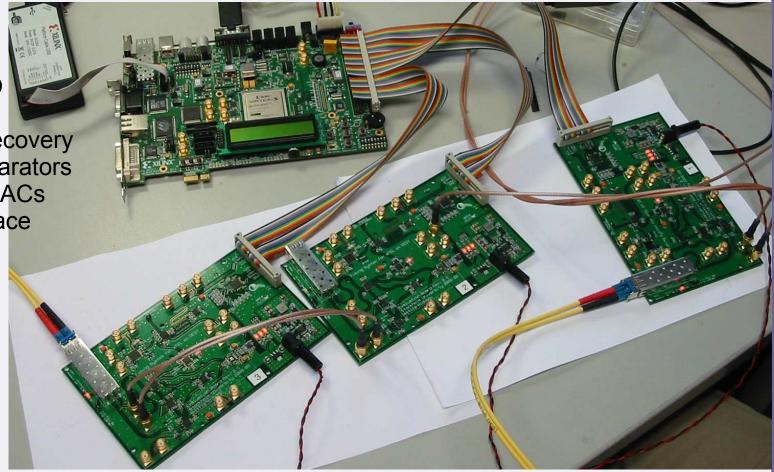

### **3 Test Boards connected to a Virtex 5**

Contains:

fiber optic IO delay chips clock data recovery phase comparators ADCs and DACs FPGA interface