FELIX Phase-II firmware specifications

ATLAS Doc.: AT2-DQ-ES-0006 EDMS Id: 2681548 v.1

ATLAS Phase-II Upgrade Project

# ATLAS FELIX firmware Phase-II Upgrade: Firmware specifications

### Abstract

This document describes the firmware specifications of the ATLAS FELIX Phase-II Upgrade Project [Collaboration:2285584].

| FELIX Phase-II firmware specifications |                                         |                                 |  |  |  |  |  |  |  |  |

|----------------------------------------|-----------------------------------------|---------------------------------|--|--|--|--|--|--|--|--|

| ATLAS Doc:                             | AT2-DQ-ES-0006                          |                                 |  |  |  |  |  |  |  |  |

| EDMS Id:                               | 2681548 v.1                             | 2681548 v.1                     |  |  |  |  |  |  |  |  |

| EDMS Url:                              | https://edms.cern.ch/document/2681548/1 |                                 |  |  |  |  |  |  |  |  |

| Version:                               | 1.037                                   |                                 |  |  |  |  |  |  |  |  |

| Created:                               | January 12, 2021                        |                                 |  |  |  |  |  |  |  |  |

| Last modified:                         | June 28, 2024                           | June 28, 2024                   |  |  |  |  |  |  |  |  |

| Prepared by:                           | Checked by:                             | Approved by:                    |  |  |  |  |  |  |  |  |

| The FELIX Team                         | The FELIX Team                          | The ATLAS review commit-<br>tee |  |  |  |  |  |  |  |  |

© 2024 CERN for the benefit of the ATLAS Collaboration.

Reproduction of this article or parts of it is allowed As specified in the CC-BY-4.0 license.

[INTENTIONALLY BLANK PAGE]

# **REVISION HISTORY**

| 0.001         2019-12-19         Frans Schreuder         Added some entities as a graphical symbol and wave-<br>forms for axi stream           0.002         2019-12-19         Frans Schreuder         Added skeleton for RD53b decoder           0.003         2019-12-20         Frans Schreuder         Added skeleton for RD53b decoder           0.004         2019-12-20         Frans Schreuder         Added skeleton for RD53b decoder and Aurora decoder in separate<br>subsections           0.006         2020-01-08         Frans Schreuder         Added block diagram of Decoding Geroups and Epaths<br>for (Ip)GBT 8b10b mode           0.008         2020-01-10         Frans Schreuder         Added block diagram of Decoding Egroups and Epaths<br>for (Ip)GBT 8b10b mode           0.009         2020-01-10         Frans Schreuder         Added block diagram for Pixel ToHost e-path           0.009         2020-01-10         Frans Schreuder         Added description of the 8b10b decoder           0.011         2020-01-13         Jacopo Pinzino         added some informations about endeavour blocks           0.012         2020-01-14         Frans Schreuder         Added description of the CB protocol           0.013         2020-01-14         Frans Schreuder         Added decoding egroup resources           0.014         2020-01-14         Frans Schreuder         Added dacoding egroup resources                                                                                  | Revision | Date       | Author(s)       | Description                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------|-----------------|------------------------------------------------------|

| 0.002         2019-12-19         Frans Schreuder         Added skeleton for RDS3b decoder           0.003         2019-12-20         Frans Schreuder         Added several blocks, entities and moved around some text           0.004         2019-12-20         Frans Schreuder         Added full mode decoder entity           0.005         2020-01-07         Frans Schreuder         Discribed the Decoding GearBox           0.007         2020-01-08         Frans Schreuder         Added block diagram of Decoding Egroups and Epaths for (Ip)(BBT 8b10b mode           0.008         2020-01-10         Frans Schreuder         Added description of the 8b10b decoder           0.010         2020-01-10         Frans Schreuder         Added description of the 8b10b decoder           0.011         2020-01-10         Frans Schreuder         Added description of the 8b10b decoder           0.011         2020-01-13         Jacopo Pinzino         added some informations about endeavour blocks           0.012         2020-01-14         Frans Schreuder         Added TTC Emulator           0.014         2020-01-14         Frans Schreuder         Added decorp resources           0.013         2020-01-14         Jacopo Pinzino         improving the Endeavour Encoder subsection           0.016         2020-01-24         Frans Schreuder         Added datas template <td>0.001</td> <td>2019-12-19</td> <td>Frans Schreuder</td> <td>Added some entities as a graphical symbol and wave-</td>   | 0.001    | 2019-12-19 | Frans Schreuder | Added some entities as a graphical symbol and wave-  |

| 0.003         2019-12-20         Frans Schreuder         Added several blocks, entities and moved around some text           0.004         2019-12-20         Frans Schreuder         Added full mode decoder entity           0.005         2020-01-07         Frans Schreuder         Split RD53b decoder and Aurora decoder in separate subsections           0.006         2020-01-08         Frans Schreuder         Added block diagram of Decoding Egroups and Epaths for (Ip)GBT 8b10b mode           0.007         2020-01-10         Frans Schreuder         Added progress bars to the different sections (Thank you LASP people for the idea)           0.010         2020-01-10         Frans Schreuder         Added some informations about endeavour blocks           0.011         2020-01-13         Jacopo Pinzino         added desome informations about endeavour blocks           0.012         2020-01-14         Frans Schreuder         Added decoding egroup resources           0.014         2020-01-14         Frans Schreuder         Added decoding egroup resources           0.016         2020-01-14         Frans Schreuder         Added decoding egroup resources           0.017         2020-01-21         Frans Schreuder         Added decoding egroup resources           0.018         2020-01-23         Frans Schreuder         Added decoding egroup resources           0.017                                                                                                           |          |            |                 | forms for axi stream                                 |

| text         Added full mode decoder entity           0.005         2020-01-07         Frans Schreuder         Split RD53b decoder and Aurora decoder in separate<br>subsections           0.006         2020-01-08         Frans Schreuder         Described the DecodingGearBox           0.007         2020-01-09         Frans Schreuder         Added block diagram of Decoding Egroups and Epaths<br>for (lp)GBT 8b10b mode           0.008         2020-01-10         Frans Schreuder         Added block diagram for Pixel ToHost e-path           0.009         2020-01-10         Frans Schreuder         Added description of the 8b10b decoder           0.011         2020-01-10         Frans Schreuder         Added description of the 8b10b decoder           0.011         2020-01-13         Jacopo Pinzino         added some informations about endeavour blocks           0.012         2020-01-14         Frans Schreuder         Added decoding egroup resources           0.013         2020-01-14         Frans Schreuder         Added description of the LCB protocol           0.014         2020-01-16         Frans Schreuder         Added description of the LCB protocol           0.017         2020-01-21         Frans Schreuder         Added description of the LCB protocol           0.018         2020-01-24         Frans Schreuder         Added description of the LCB protocol </td <td>0.002</td> <td>2019-12-19</td> <td>Frans Schreuder</td> <td>Added skeleton for RD53b decoder</td> | 0.002    | 2019-12-19 | Frans Schreuder | Added skeleton for RD53b decoder                     |

| 0.004         2019-12-20         Frans Schreuder         Added full mode decoder entity           0.005         2020-01-07         Frans Schreuder         Split RD53b decoder and Aurora decoder in separate subsections           0.006         2020-01-08         Frans Schreuder         Described the DecodingGearBox           0.007         2020-01-09         Frans Schreuder         Added block diagram of Decoding Egroups and Epaths for (Ip)GBT 8b10b mode           0.008         2020-01-10         Frans Schreuder         Added progress bars to the different sections (Thank you LASP people for the idea)           0.010         2020-01-13         Jacopo Pinzino         added some informations about endeavour blocks           0.012         2020-01-14         Frans Schreuder         Added decoding egroup resources           0.012         2020-01-14         Frans Schreuder         Added decoding egroup resources           0.016         2020-01-14         Frans Schreuder         Added decoding egroup resources           0.016         2020-01-21         Elena Zhivun         Added decoding egroup resources           0.018         2020-01-24         Frans Schreuder         Added decoder           0.018         2020-01-24         Frans Schreuder         Added decoder           0.016         2020-01-24         Frans Schreuder         Added decoding egro                                                                                                                        | 0.003    | 2019-12-20 | Frans Schreuder | Added several blocks, entities and moved around some |

| 0.005         2020-01-07         Frans Schreuder         Split RD53b decoder and Aurora decoder in separate<br>subsections           0.006         2020-01-08         Frans Schreuder         Described the DecodingGearBox           0.007         2020-01-09         Frans Schreuder         Added block diagram for Pixel ToHost e-path           0.008         2020-01-10         Frans Schreuder         Added description of the 8b10b decoder           0.009         2020-01-10         Frans Schreuder         Added description of the 8b10b decoder           0.011         2020-01-13         Jacopo Pinzino         added some informations about endeavour blocks           0.012         2020-01-14         Frans Schreuder         Added ToT Emulator           0.013         2020-01-14         Frans Schreuder         Added decoding egroup resources           0.014         2020-01-14         Frans Schreuder         Added decoding egroup resources           0.015         2020-01-14         Frans Schreuder         Added decoding egroup resources           0.016         2020-01-23         Frans Schreuder         Added description of the LCB protocol           0.018         2020-01-24         Frans Schreuder         Added description about CRC polynomial in<br>FullMode.pdf           0.021         2020-01-27         Marius Wensing         statring work on the RD53B Deco                                                                                                                  |          |            |                 |                                                      |

| subsections           0.006         2020-01-08         Frans Schreuder         Described the Decoding GearBox           0.007         2020-01-09         Frans Schreuder         Added block diagram of Decoding Egroups and Epaths<br>for (Ip)GBT 8b10b mode           0.008         2020-01-10         Frans Schreuder         Added block diagram for Pixel ToHost e-path           0.009         2020-01-10         Frans Schreuder         Added progress bars to the different sections (Thank you<br>LASP people for the idea)           0.011         2020-01-14         Frans Schreuder         Added some informations about endeavour blocks           0.012         2020-01-14         Frans Schreuder         Added some missing encoder (skeleton) tex files           0.013         2020-01-16         Frans Schreuder         Added decoding egroup resources           0.014         2020-01-16         Frans Schreuder         regenerated pdf           0.017         2020-01-23         Frans Schreuder         regenerated pdf           0.018         2020-01-24         Frans Schreuder         Chaged information about CRC polynomial in<br>FullMode.pdf           0.020         2020-01-27         Marius Wensing         statring work on the RD53B Decoder           0.021         2020-01-28         Frans Schreuder         Replaced verbatim with Istitisting in LCBEncoder.tex, it<br>gave typesetting errors                                                                                           |          |            |                 |                                                      |

| 0.006         2020-01-08         Frans Schreuder         Described the DecodingGearBox           0.007         2020-01-09         Frans Schreuder         Added block diagram of Decoding Egroups and Epaths for (Ip)GBT 8b10b mode           0.008         2020-01-10         Frans Schreuder         Added block diagram for Pixel ToHost e-path           0.009         2020-01-10         Frans Schreuder         Added block diagram for Pixel ToHost e-path           0.010         2020-01-10         Frans Schreuder         Added progress bars to the different sections (Thank you LASP people for the idea)           0.011         2020-01-14         Frans Schreuder         Added TC Emulator           0.012         2020-01-14         Frans Schreuder         Added TC Emulator           0.014         2020-01-14         Frans Schreuder         Added decoding egroup resources           0.016         2020-01-12         Frans Schreuder         Added description of the LCB protocol           0.016         2020-01-23         Frans Schreuder         Added description of the LCB protocol           0.018         2020-01-24         Frans Schreuder         Added description about CRC polynomial in FullMode,pdf           0.021         2020-01-28         Frans Schreuder         Replaced verbatim with Istilisting in LCBEncoder.tx, it gave typesetting errors           0.022         2020-0                                                                                                      | 0.005    | 2020-01-07 | Frans Schreuder | Split RD53b decoder and Aurora decoder in separate   |

| 0.007         2020-01-09         Frans Schreuder         Added block diagram of Decoding Egroups and Epaths<br>for (Ip)GBT 8b10b mode           0.008         2020-01-10         Frans Schreuder         Added block diagram for Pixel ToHost e-path           0.009         2020-01-10         Frans Schreuder         Added block diagram for Pixel ToHost e-path           0.010         2020-01-10         Frans Schreuder         Added description of the 8b10b decoder           0.011         2020-01-13         Jacopo Pinzino         added some informations about endeavour blocks           0.012         2020-01-14         Frans Schreuder         Added TC Emulator           0.014         2020-01-14         Frans Schreuder         Added decoding egroup resources           0.015         2020-01-16         Frans Schreuder         Added decoding egroup resources           0.016         2020-01-12         Frans Schreuder         Added decoding egroup resources           0.017         2020-01-23         Frans Schreuder         Chadged atlas template           0.018         2020-01-24         Frans Schreuder         Chadged verbatim with Istilisting in LCBEncoder.tex, it gave typeseting errors           0.021         2020-01-27         Marius Wensing         starting work on the RD53B Decoder           0.022         2020-02-04         Marius Wensing         add                                                                                                                     |          |            |                 |                                                      |

| for (Ip)GBT 8b10b mode           0.008         2020-01-10         Frans Schreuder         Added block diagram for Pixel ToHost e-path           0.009         2020-01-10         Frans Schreuder         Added description of the 8b10b decoder           0.011         2020-01-10         Frans Schreuder         Added progress bars to the different sections (Thank you LASP people for the idea)           0.011         2020-01-14         Frans Schreuder         Added some informations about endeavour blocks           0.012         2020-01-14         Frans Schreuder         Added dosme informations about endeavour blocks           0.012         2020-01-14         Frans Schreuder         Added description of the LCB protocol           0.016         2020-01-16         Frans Schreuder         Added description of the LCB protocol           0.016         2020-01-27         Frans Schreuder         Added description of the LCB protocol           0.018         2020-01-28         Frans Schreuder         Added description of the RD53B Decoder           0.020         2020-01-27         Marius Wensing         starting work on the RD53B Decoder           0.021         2020-01-28         Frans Schreuder         Replaced verbatim with Istlisting in LCBEncoder.tex, it gave typesetting errors           0.022         2020-02-04         Marius Wensing         adding entity for FromHost Centra                                                                                             |          |            |                 |                                                      |

| 0.009         2020-01-10         Frans Schreuder         Added description of the 8b10b decoder           0.010         2020-01-10         Frans Schreuder         Added progress bars to the different sections (Thank you LASP people for the idea)           0.011         2020-01-13         Jacopo Pinzino         added some informations about endeavour blocks           0.012         2020-01-14         Frans Schreuder         Added some missing encoder (skeleton) tex files           0.013         2020-01-16         Frans Schreuder         Added decoding egroup resources           0.014         2020-01-16         Frans Schreuder         Added description of the LCB protocol           0.015         2020-01-16         Frans Schreuder         regenerated pdf           0.017         2020-01-23         Frans Schreuder         Added description of the LCB protocol           0.018         2020-01-24         Frans Schreuder         Changed information about CRC polynomial in FullMode.pdf           0.020         2020-01-27         Marius Wensing         starting work on the RD53B Decoder           0.021         2020-01-28         Frans Schreuder         Replaced verbatim with Ististing in LCBEncoder.tex, it gave typesetting errors           0.022         2020-02-04         Marius Wensing         adding entity for FromHost Central Router           0.023         2020-02-0                                                                                                      | 0.007    | 2020-01-09 | Frans Schreuder |                                                      |

| 0.010         2020-01-10         Frans Schreuder         Added progress bars to the different sections (Thank you LASP people for the idea)           0.011         2020-01-13         Jacopo Pinzino         added some informations about endeavour blocks           0.012         2020-01-14         Frans Schreuder         Added some missing encoder (skeleton) tex files           0.013         2020-01-14         Frans Schreuder         Added decoding egroup resources           0.014         2020-01-16         Frans Schreuder         regenerated pdf           0.017         2020-01-21         Elena Zhivun         Added description of the LCB protocol           0.018         2020-01-23         Frans Schreuder         Added atlas template           0.019         2020-01-24         Frans Schreuder         Added atlas template           0.020         2020-01-27         Marius Wensing         starting work on the RD53B Decoder           0.021         2020-01-28         Frans Schreuder         Replaced verbatim with Istlisting in LCBEncoder.tex, it gave typesetting errors           0.022         2020-01-24         Marius Wensing         adding entity for FromHost Central Router           0.021         2020-02-04         Marius Wensing         adding entity for FromHost Central Router           0.022         2020-02-10         Marius Wensing         ad                                                                                                                        | 0.008    | 2020-01-10 | Frans Schreuder | Added block diagram for Pixel ToHost e-path          |

| LASP people for the idea)0.0112020-01-13Jacopo Pinzinoadded some informations about endeavour blocks0.0122020-01-14Frans SchreuderAdded some missing encoder (skeleton) tex files0.0132020-01-14Frans SchreuderAdded decoding egroup resources0.0142020-01-16Frans SchreuderAdded decording egroup resources0.0152020-01-16Frans SchreuderAdded description of the LCB protocol0.0162020-01-21Elena ZhivunAdded datas template0.0172020-01-23Frans SchreuderAdded description of the LCB protocol0.0182020-01-24Frans SchreuderChanged information about CRC polynomial in<br>FullMode.pdf0.0202020-01-27Marius Wensingstarting work on the RD53B Decoder0.0212020-01-28Frans SchreuderReplaced verbatim with Ististing in LCBEncoder.tex, it<br>gave typesetting errors0.0222020-02-04Marius Wensingadding entity for FromHost Central Router0.0232020-02-04Marius Wensingmore work on the RD53B decoder section0.0242020-02-01Marius Wensingadding example waveform for CRFromHost Input0.0252020-02-10Marius Wensingadding example waveform for CRFromHost Input0.0262020-02-11Frans SchreuderRegenerated wupper documentation with rm4.90.0272020-02-11Marius Wensingadding example waveform for CRFromHost Input0.0282020-02-11Marius Wensingadding resource usage for RD53B decoder0.02                                                                                                                                                                                                                                           | 0.009    | 2020-01-10 | Frans Schreuder | Added description of the 8b10b decoder               |

| 0.011         2020-01-13         Jacopo Pinzino         added some informations about endeavour blocks           0.012         2020-01-14         Frans Schreuder         Added some missing encoder (skeleton) tex files           0.013         2020-01-14         Frans Schreuder         Added TC Emulator           0.014         2020-01-16         Frans Schreuder         Added decoding egroup resources           0.015         2020-01-16         Frans Schreuder         Added description of the LCB protocol           0.018         2020-01-23         Frans Schreuder         Added datas template           0.019         2020-01-24         Frans Schreuder         Changed information about CRC polynomial in FullMode.pdf           0.020         2020-01-27         Marius Wensing         starting work on the RD53B Decoder           0.021         2020-01-28         Frans Schreuder         Replaced verbatim with Istlisting in LCBEncoder.tex, it gave typesetting errors           0.022         2020-02-04         Marius Wensing         updating RD53B decoder entity and re-generated PDF           0.024         2020-02-04         Marius Wensing         more work on the RD53B decoder section           0.024         2020-02-04         Jacopo Pinzino         adding entity for FromHost Central Router           0.025         2020-02-10         Marus Wensing <t< td=""><td>0.010</td><td>2020-01-10</td><td>Frans Schreuder</td><td></td></t<>                                             | 0.010    | 2020-01-10 | Frans Schreuder |                                                      |

| 0.0122020-01-14Frans SchreuderAdded some missing encoder (skeleton) tex files0.0132020-01-14Frans SchreuderAdded TTC Emulator0.0142020-01-14Jacopo Pinzinoimproving the Endeavour Encoder subsection0.0152020-01-16Frans SchreuderAdded decoding egroup resources0.0162020-01-21Elena ZhivunAdded description of the LCB protocol0.0182020-01-23Frans SchreuderAdded attas template0.0192020-01-24Frans SchreuderChanged information about CRC polynomial in<br>FullMode.pdf0.0202020-01-27Marius Wensingstarting work on the RD53B Decoder0.0212020-01-28Frans SchreuderReplaced verbatim with Istlisting in LCBEncoder.tex, it<br>gave typesetting errors0.0222020-02-04Marius Wensingadding entity for FromHost Central Router0.0242020-02-04Marius Wensingmore work on the RD53B decoder section0.0252020-02-10Marius Wensingmore work on the RD53B decoder section0.0262020-02-10Marius Wensingadding example waveform for CRFromHost input0.0272020-02-11Frans SchreuderRegenerated wupper documentation with rm4.90.0282020-02-17Marius Wensingadding example waveform for CRFromHost input0.0292020-02-17Marius Wensingadding resource usage for RD53B decoder0.0312020-02-20Frans SchreuderFixed some issues in the EndeavourDecoder/Encoder0.0322020-02-17Marius Wensingad                                                                                                                                                                                                                                                    | 0.011    | 2020-01-13 | Jacopo Pinzino  |                                                      |

| 0.0132020-01-14Frans SchreuderAdded TTC Emulator0.0142020-01-14Jacopo Pinzinoimproving the Endeavour Encoder subsection0.0152020-01-16Frans SchreuderAdded decoding egroup resources0.0162020-01-21Elena ZhivunAdded description of the LCB protocol0.0172020-01-21Elena ZhivunAdded description of the LCB protocol0.0182020-01-23Frans SchreuderAdded description of the LCB protocol0.0192020-01-24Frans SchreuderChanged information about CRC polynomial in<br>FullMode.pdf0.0202020-01-27Marius Wensingstarting work on the RD53B Decoder0.0212020-01-28Frans SchreuderReplaced verbatim with Istlisting in LCBEncoder.tex, it<br>gave typesetting errors0.0222020-02-04Marius Wensingupdating RD53B decoder entity and re-generated PDF0.0232020-02-04Marius Wensingmore work on the RD53B decoder section0.0242020-02-10Jacopo Pinzinoadding entity for FromHost Central Router0.0252020-02-11Frans SchreuderRegenerated wupper documentation with rm4.90.0262020-02-17Marius Wensingadding resource usage for RD53B decoder0.0292020-02-18Marius Wensingadding resource usage for RD53B decoder0.0312020-02-20Frans SchreuderFried some issues in the EndeavourDecoder/Encoder0.0322020-02-20Frans SchreuderFreese string regenerated pdf0.0332020-02-20Frans SchreuderSome                                                                                                                                                                                                                                                    |          |            |                 |                                                      |

| 0.0142020-01-14Jacopo Pinzinoimproving the Endeavour Encoder subsection0.0152020-01-16Frans SchreuderAdded decoding egroup resources0.0162020-01-21Elena ZhivunAdded description of the LCB protocol0.0182020-01-23Frans SchreuderAdded atlas template0.0192020-01-24Frans SchreuderChanged information about CRC polynomial in<br>FullMode.pdf0.0202020-01-27Marius Wensingstarting work on the RD53B Decoder0.0212020-01-28Frans SchreuderReplaced verbatim with Istlisting in LCBEncoder.tex, it<br>gave typesetting errors0.0222020-02-04Marius Wensingupdating RD53B decoder entity and re-generated PDF0.0232020-02-04Marius Wensingadding entity for FromHost Central Router0.0242020-02-04Jacopo Pinzinoimprovement endeavour encoder decoder part0.0252020-02-10Marius Wensingmore work on the RD53B decoder section0.0262020-02-11Frans SchreuderRegenerated wupper documentation with rm4.90.0282020-02-17Marius Wensingadding example waveform for CRFromHost input0.0312020-02-18Marius Wensingadding resource usage for RD53B decoder0.0312020-02-20Frans SchreuderFixed some issues in the Endeavour Decoder/Encoder0.0322020-02-20Frans SchreuderFixed some issues in the Endeavour Decoder/Encoder0.0332020-02-20Frans SchreuderSome minor updates to Endeavour Decoder / Encoder0.034 <td< td=""><td></td><td></td><td></td><td>- · · · · · · · · · · · · · · · · · · ·</td></td<>                                                                                                                                    |          |            |                 | - · · · · · · · · · · · · · · · · · · ·              |

| 0.0152020-01-16Frans SchreuderAdded decoding egroup resources0.0162020-01-21Frans Schreuderregenerated pdf0.0172020-01-23Frans SchreuderAdded description of the LCB protocol0.0182020-01-23Frans SchreuderAdded atlas template0.0192020-01-24Frans SchreuderChanged information about CRC polynomial in<br>FullMode.pdf0.0202020-01-27Marius Wensingstarting work on the RD53B Decoder0.0212020-01-28Frans SchreuderReplaced verbatim with Istlisting in LCBEncoder.tex, it<br>gave typesetting errors0.0222020-02-04Marius Wensingupdating RD53B decoder entity and re-generated PDF0.0232020-02-04Jacopo Pinzinoadding entity for FromHost Central Router0.0242020-02-04Jacopo Pinzinoimprovement endeavour encoder decoder part0.0252020-02-10Marius Wensingmore work on the RD53B decoder section0.0262020-02-11Frans SchreuderRegenerated wupper documentation with rm4.90.0282020-02-17Marius Wensingadding example waveform for CRFromHost Central Router0.0292020-02-18Marius Wensingadding resource usage for RD53B decoder0.0302020-02-20Frans SchreuderFixed some issues in the EndeavourDecoder/Encoder<br>document the fromHost Central Router0.0312020-02-20Frans SchreuderFixed some issues in the Endeavour Decoder/Encoder0.0322020-02-20Frans SchreuderSome issues in the Endeavour Decoder/Encoder                                                                                                                                                                                                                  |          |            |                 |                                                      |

| 0.0162020-01-16Frans Schreuderregenerated pdf0.0172020-01-21Elena ZhivunAdded description of the LCB protocol0.0182020-01-23Frans SchreuderAdded atlas template0.0192020-01-24Frans SchreuderChanged information about CRC polynomial in<br>FullMode.pdf0.0202020-01-27Marius Wensingstarting work on the RD53B Decoder0.0212020-01-28Frans SchreuderReplaced verbatim with Istlisting in LCBEncoder.tex, it<br>gave typesetting errors0.0222020-02-04Marius Wensingadding entity for FromHost Central Router0.0242020-02-04Jacopo Pinzinoadd table0.0252020-02-04Marius Wensingmore work on the RD53B decoder section0.0242020-02-10Marius Wensingmore work on the RD53B decoder section0.0252020-02-10Jacopo Pinzinoimprovement endeavour encoder decoder part0.0272020-02-17Marius Wensingadding example waveform for CRFromHost input0.0282020-02-17Marius Wensingstarting to document the FromHost Central Router0.0302020-02-17Marius Wensingadding resource usage for RD53B decoder0.0312020-02-20Frans SchreuderFixed some issues in the EndeavourDecoder/Encoder0.0312020-02-20Frans Schreuderregenerated pdf0.0322020-02-20Frans Schreuderregenerated pdf0.0332020-02-20Frans Schreuderregenerated pdf0.0342020-02-20Frans Schreuder </td <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                             |          |            |                 |                                                      |

| 0.0182020-01-23Frans SchreuderAdded atlas template0.0192020-01-24Frans SchreuderChanged information about CRC polynomial in<br>FullMode.pdf0.0202020-01-27Marius Wensingstarting work on the RD53B Decoder0.0212020-01-28Frans SchreuderReplaced verbatim with Istlisting in LCBEncoder.tex, it<br>gave typesetting errors0.0222020-02-04Marius Wensingupdating RD53B decoder entity and re-generated PDF0.0232020-02-04Marius Wensingadding entity for FromHost Central Router0.0242020-02-04Jacopo Pinzinoadd table0.0252020-02-10Marius Wensingmore work on the RD53B decoder section0.0262020-02-11Frans SchreuderRegenerated wupper documentation with rm4.90.0272020-02-11Marius Wensingadding example waveform for CRFromHost input0.0282020-02-17Marius Wensingadding resource usage for RD53B decoder0.0302020-02-18Marius Wensingadding resource usage for RD53B decoder0.0312020-02-20Frans SchreuderFixed some issues in the EndeavourDecoder/Encoder0.0322020-02-20Frans Schreuderregenerated pdf0.0332020-02-20Frans Schreudersome inforue tot Unified tables through-<br>out the document0.0342020-02-20Frans SchreuderSome minor updates to Endeavour Decoder / Encoder0.0352020-03-17Frans SchreuderAdded section about TTC Encoder0.0362020-05-07jacopo pinzinoad                                                                                                                                                                                                                                                     | 0.016    | 2020-01-16 | Frans Schreuder | ÷ • 1                                                |

| 0.0192020-01-24Frans SchreuderChanged information about CRC polynomial in<br>FullMode.pdf0.0202020-01-27Marius Wensingstarting work on the RD53B Decoder0.0212020-01-28Frans SchreuderReplaced verbatim with Istlisting in LCBEncoder.tex, it<br>gave typesetting errors0.0222020-02-04Marius Wensingupdating RD53B decoder entity and re-generated PDF0.0232020-02-04Marius Wensingadding entity for FromHost Central Router0.0242020-02-04Jacopo Pinzinoadd table0.0252020-02-10Marius Wensingmore work on the RD53B decoder section0.0262020-02-11Frans SchreuderRegenerated wupper documentation with rm4.90.0272020-02-17Marius Wensingadding example waveform for CRFromHost input0.0282020-02-17Marius Wensingstarting to document the FromHost Central Router0.0302020-02-18Marius Wensingadding resource usage for RD53B decoder0.0312020-02-20Frans SchreuderFixed some issues in the EndeavourDecoder/Encoder0.0332020-02-20Frans Schreudercentrated pdf0.0342020-02-21Frans SchreuderSome minor updates to Endeavour Decoder / Encoder0.0352020-03-17Frans SchreuderSome minor updates to Endeavour Decoder / Encoder0.0342020-02-20Frans SchreuderSome minor updates to Endeavour Decoder / Encoder0.0352020-03-17Frans SchreuderAdded section about TTC Encoder0.0362020-05-07j                                                                                                                                                                                                                                           | 0.017    | 2020-01-21 | Elena Zhivun    | Added description of the LCB protocol                |

| 0.0192020-01-24Frans SchreuderChanged information about CRC polynomial in<br>FullMode.pdf0.0202020-01-27Marius Wensingstarting work on the RD53B Decoder0.0212020-01-28Frans SchreuderReplaced verbatim with Istlisting in LCBEncoder.tex, it<br>gave typesetting errors0.0222020-02-04Marius Wensingupdating RD53B decoder entity and re-generated PDF0.0232020-02-04Marius Wensingadding entity for FromHost Central Router0.0242020-02-04Jacopo Pinzinoadd table0.0252020-02-10Marius Wensingmore work on the RD53B decoder section0.0262020-02-11Frans SchreuderRegenerated wupper documentation with rm4.90.0272020-02-17Marius Wensingadding example waveform for CRFromHost input0.0282020-02-17Marius Wensingstarting to document the FromHost Central Router0.0302020-02-18Marius Wensingadding resource usage for RD53B decoder0.0312020-02-20Frans SchreuderFixed some issues in the EndeavourDecoder/Encoder0.0332020-02-20Frans Schreudercentrated pdf0.0342020-02-21Frans SchreuderSome minor updates to Endeavour Decoder / Encoder0.0352020-03-17Frans SchreuderSome minor updates to Endeavour Decoder / Encoder0.0342020-02-20Frans SchreuderSome minor updates to Endeavour Decoder / Encoder0.0352020-03-17Frans SchreuderAdded section about TTC Encoder0.0362020-05-07j                                                                                                                                                                                                                                           | 0.018    | 2020-01-23 | Frans Schreuder | Added atlas template                                 |

| 0.0202020-01-27Marius Wensingstarting work on the RD53B Decoder0.0212020-01-28Frans SchreuderReplaced verbatim with Istlisting in LCBEncoder.tex, it<br>gave typesetting errors0.0222020-02-04Marius Wensingupdating RD53B decoder entity and re-generated PDF0.0232020-02-04Marius Wensingadding entity for FromHost Central Router0.0242020-02-04Jacopo Pinzinoadd table0.0252020-02-10Marius Wensingmore work on the RD53B decoder section0.0262020-02-10Jacopo Pinzinoimprovement endeavour encoder decoder part0.0272020-02-11Frans SchreuderRegenerated wupper documentation with rm4.90.0282020-02-17Marius Wensingadding example waveform for CRFromHost input0.0292020-02-17Marius Wensingadding resource usage for RD53B decoder0.0302020-02-18Marius Wensingadding resource usage for RD53B decoder0.0312020-02-20Frans SchreuderFixed some issues in the EndeavourDecoder/Encoder0.0322020-02-20Jacopo Pinzinoimprovement endeavour encoder decoder part0.0332020-02-21Frans SchreuderSome minor updates to Endeavour Decoder / Encoder0.0342020-02-21Frans SchreuderSome minor updates to Endeavour Decoder / Encoder0.0352020-03-17Frans SchreuderAdded section about TTC Encoder0.0362020-05-07jacopo pinzinoadded EndeavourDecider subsection of the Phase2_FM_specs0.0372020-05-07 <td>0.019</td> <td>2020-01-24</td> <td>Frans Schreuder</td> <td>Changed information about CRC polynomial in</td>                                                                                                                    | 0.019    | 2020-01-24 | Frans Schreuder | Changed information about CRC polynomial in          |

| 0.0212020-01-28Frans Schreuder<br>and SchreuderReplaced verbatim with Istlisting in LCBEncoder.tex, it<br>gave typesetting errors0.0222020-02-04Marius Wensingupdating RD53B decoder entity and re-generated PDF0.0232020-02-04Marius Wensingadding entity for FromHost Central Router0.0242020-02-04Jacopo Pinzinoadd table0.0252020-02-10Marius Wensingmore work on the RD53B decoder section0.0262020-02-10Jacopo Pinzinoimprovement endeavour encoder decoder part0.0272020-02-11Frans SchreuderRegenerated wupper documentation with rm4.90.0282020-02-17Marius Wensingadding example waveform for CRFromHost input0.0292020-02-18Marius Wensingadding resource usage for RD53B decoder0.0302020-02-20Frans SchreuderFixed some issues in the EndeavourDecoder/Encoder<br>documents (figures not found etc) Unified tables through-<br>out the document0.0322020-02-20Jacopo Pinzinoimprovement endeavour Decoder / Encoder0.0332020-02-20Frans SchreuderSome minor updates to Endeavour Decoder / Encoder0.0342020-02-21Frans SchreuderSome minor updates to Endeavour Decoder / Encoder0.0352020-02-17Jacopo pinzinoadded EndeavourDeglitcher in the Endeavour Decoder0.0362020-02-19jacopo pinzinoadded EndeavourDeglitcher in the Endeavour Decoder0.0372020-02-07jacopo pinzinocorrect typo in Endeavour Decoder subsection of the<br>Phase2_FM_specs </td <td></td> <td></td> <td></td> <td>FullMode.pdf</td>                                                                                                                |          |            |                 | FullMode.pdf                                         |

| 0.0222020-02-04Marius Wensingupdating RD53B decoder entity and re-generated PDF0.0232020-02-04Marius Wensingadding entity for FromHost Central Router0.0242020-02-04Jacopo Pinzinoadd table0.0252020-02-10Marius Wensingmore work on the RD53B decoder section0.0262020-02-10Jacopo Pinzinoimprovement endeavour encoder decoder part0.0272020-02-11Frans SchreuderRegenerated wupper documentation with rm4.90.0282020-02-17Marius Wensingadding example waveform for CRFromHost input0.0292020-02-17Marius Wensingstarting to document the FromHost Central Router0.0302020-02-18Marius Wensingadding resource usage for RD53B decoder0.0312020-02-20Frans SchreuderFixed some issues in the EndeavourDecoder/Encoder<br>documents (figures not found etc) Unified tables through-<br>out the document0.0322020-02-20Frans Schreuderregenerated pdf0.0332020-02-21Frans SchreuderSome minor updates to Endeavour Decoder / Encoder0.0342020-02-21Frans SchreuderAdded section about TTC Encoder0.0352020-03-17Frans SchreuderAdded section about TTC Encoder0.0362020-05-07jacopo pinzinoadded EndeavourDecider subsection of the Phase2_FM_specs0.0372020-05-07jacopo pinzinocorrect typo in Endeavour Decoder subsection of the Phase2_FM_specs                                                                                                                                                                                                                                                                                     |          |            | v               | -                                                    |

| 0.0232020-02-04Marius Wensing<br>Jacopo Pinzinoadding entity for FromHost Central Router0.0242020-02-04Jacopo Pinzinoadd table0.0252020-02-10Marius Wensingmore work on the RD53B decoder section0.0262020-02-10Jacopo Pinzinoimprovement endeavour encoder decoder part0.0272020-02-11Frans SchreuderRegenerated wupper documentation with rm4.90.0282020-02-17Marius Wensingadding example waveform for CRFromHost input0.0292020-02-17Marius Wensingstarting to document the FromHost Central Router0.0302020-02-18Marius Wensingadding resource usage for RD53B decoder0.0312020-02-20Frans SchreuderFixed some issues in the EndeavourDecoder/Encoder<br>documents (figures not found etc) Unified tables through-<br>out the document0.0322020-02-20Jacopo Pinzinoimprovement endeavour encoder decoder part0.0332020-02-20Frans Schreuderregenerated pdf0.0342020-02-21Frans SchreuderSome minor updates to Endeavour Decoder / Encoder0.0352020-03-17Frans SchreuderAdded section about TTC Encoder0.0362020-05-07jacopo pinzinoadded Endeavour Decoder subsection of the Phase2_FM_specs0.0372020-05-07jacopo pinzinocorrect typo in Endeavour Decoder subsection of the Phase2_FM_specs                                                                                                                                                                                                                                                                                                                                       | 0.021    | 2020-01-28 | Frans Schreuder |                                                      |

| 0.0242020-02-04Jacopo Pinzinoadd table0.0252020-02-10Marius Wensingmore work on the RD53B decoder section0.0262020-02-10Jacopo Pinzinoimprovement endeavour encoder decoder part0.0272020-02-11Frans SchreuderRegenerated wupper documentation with rm4.90.0282020-02-17Marius Wensingadding example waveform for CRFromHost input0.0292020-02-17Marius Wensingstarting to document the FromHost Central Router0.0302020-02-18Marius Wensingadding resource usage for RD53B decoder0.0312020-02-20Frans SchreuderFixed some issues in the EndeavourDecoder/Encoder<br>documents (figures not found etc) Unified tables through-<br>out the document0.0322020-02-20Jacopo Pinzinoimprovement endeavour encoder decoder part0.0332020-02-21Frans Schreuderregenerated pdf0.0342020-02-21Frans SchreuderSome minor updates to Endeavour Decoder / Encoder0.0352020-03-17Frans SchreuderAdded section about TTC Encoder0.0362020-05-07jacopo pinzinoadded EndeavourDeglitcher in the Endeavour Decoder0.0372020-05-07jacopo pinzinocorrect typo in Endeavour Decoder subsection of the<br>Phase2_FM_specs                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0.022    | 2020-02-04 | Marius Wensing  | updating RD53B decoder entity and re-generated PDF   |

| 0.0252020-02-10Marius Wensingmore work on the RD53B decoder section0.0262020-02-10Jacopo Pinzinoimprovement endeavour encoder decoder part0.0272020-02-11Frans SchreuderRegenerated wupper documentation with rm4.90.0282020-02-17Marius Wensingadding example waveform for CRFromHost input0.0292020-02-17Marius Wensingstarting to document the FromHost Central Router0.0302020-02-18Marius Wensingadding resource usage for RD53B decoder0.0312020-02-20Frans SchreuderFixed some issues in the EndeavourDecoder/Encoder<br>documents (figures not found etc) Unified tables through-<br>out the document0.0322020-02-20Jacopo Pinzinoimprovement endeavour encoder decoder part0.0332020-02-20Frans Schreuderregenerated pdf0.0342020-02-21Frans SchreuderSome minor updates to Endeavour Decoder / Encoder0.0352020-03-17Frans SchreuderAdded section about TTC Encoder0.0362020-05-07jacopo pinzinoadded EndeavourDeglitcher in the Endeavour Decoder0.0372020-05-07jacopo pinzinocorrect typo in Endeavour Decoder subsection of the<br>Phase2_FM_specs                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0.023    | 2020-02-04 | Marius Wensing  | adding entity for FromHost Central Router            |

| 0.0262020-02-10Jacopo Pinzinoimprovement endeavour encoder decoder part0.0272020-02-11Frans SchreuderRegenerated wupper documentation with rm4.90.0282020-02-17Marius Wensingadding example waveform for CRFromHost input0.0292020-02-17Marius Wensingstarting to document the FromHost Central Router0.0302020-02-18Marius Wensingadding resource usage for RD53B decoder0.0312020-02-20Frans SchreuderFixed some issues in the EndeavourDecoder/Encoder<br>documents (figures not found etc) Unified tables through-<br>out the document0.0322020-02-20Jacopo Pinzinoimprovement endeavour encoder decoder part0.0332020-02-20Frans Schreuderregenerated pdf0.0342020-02-21Frans SchreuderSome minor updates to Endeavour Decoder / Encoder0.0352020-03-17Frans SchreuderAdded section about TTC Encoder0.0362020-05-07jacopo pinzinoadded EndeavourDeglitcher in the Endeavour Decoder0.0372020-05-07jacopo pinzinocorrect typo in Endeavour Decoder subsection of the<br>Phase2_FM_specs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0.024    | 2020-02-04 | Jacopo Pinzino  | add table                                            |

| 0.0272020-02-11Frans SchreuderRegenerated wupper documentation with rm4.90.0282020-02-17Marius Wensingadding example waveform for CRFromHost input0.0292020-02-17Marius Wensingstarting to document the FromHost Central Router0.0302020-02-18Marius Wensingadding resource usage for RD53B decoder0.0312020-02-20Frans SchreuderFixed some issues in the EndeavourDecoder/Encoder<br>documents (figures not found etc) Unified tables through-<br>out the document0.0322020-02-20Jacopo Pinzinoimprovement endeavour encoder decoder part0.0332020-02-20Frans Schreuderregenerated pdf0.0342020-02-21Frans SchreuderSome minor updates to Endeavour Decoder / Encoder0.0362020-03-17Frans SchreuderAdded section about TTC Encoder0.0372020-05-07jacopo pinzinocorrect typo in Endeavour Decoder subsection of the<br>Phase2_FM_specs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0.025    | 2020-02-10 | Marius Wensing  | more work on the RD53B decoder section               |

| 0.0282020-02-17Marius Wensingadding example waveform for CRFromHost input0.0292020-02-17Marius Wensingstarting to document the FromHost Central Router0.0302020-02-18Marius Wensingadding resource usage for RD53B decoder0.0312020-02-20Frans SchreuderFixed some issues in the EndeavourDecoder/Encoder<br>documents (figures not found etc) Unified tables through-<br>out the document0.0322020-02-20Jacopo Pinzinoimprovement endeavour encoder decoder part0.0332020-02-20Frans Schreuderregenerated pdf0.0342020-02-21Frans SchreuderSome minor updates to Endeavour Decoder / Encoder0.0352020-03-17Frans SchreuderAdded section about TTC Encoder0.0362020-05-07jacopo pinzinoadded EndeavourDeglitcher in the Endeavour Decoder0.0372020-05-07jacopo pinzinocorrect typo in Endeavour Decoder subsection of the<br>Phase2_FM_specs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0.026    | 2020-02-10 | Jacopo Pinzino  | improvement endeavour encoder decoder part           |

| 0.0292020-02-17Marius Wensingstarting to document the FromHost Central Router0.0302020-02-18Marius Wensingadding resource usage for RD53B decoder0.0312020-02-20Frans SchreuderFixed some issues in the EndeavourDecoder/Encoder<br>documents (figures not found etc) Unified tables through-<br>out the document0.0322020-02-20Jacopo Pinzinoimprovement endeavour encoder decoder part0.0332020-02-20Frans Schreuderregenerated pdf0.0342020-02-21Frans SchreuderSome minor updates to Endeavour Decoder / Encoder0.0352020-03-17Frans SchreuderAdded section about TTC Encoder0.0362020-05-07jacopo pinzinoadded EndeavourDeglitcher in the Endeavour Decoder0.0372020-05-07jacopo pinzinocorrect typo in Endeavour Decoder subsection of the<br>Phase2_FM_specs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0.027    | 2020-02-11 | Frans Schreuder | Regenerated wupper documentation with rm4.9          |

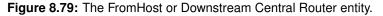

| 0.0302020-02-18Marius Wensingadding resource usage for RD53B decoder0.0312020-02-20Frans SchreuderFixed some issues in the EndeavourDecoder/Encoder<br>documents (figures not found etc) Unified tables through-<br>out the document0.0322020-02-20Jacopo Pinzinoimprovement endeavour encoder decoder part0.0332020-02-20Frans Schreuderregenerated pdf0.0342020-02-21Frans SchreuderSome minor updates to Endeavour Decoder / Encoder0.0352020-03-17Frans SchreuderAdded section about TTC Encoder0.0362020-05-07jacopo pinzinoadded EndeavourDeglitcher in the Endeavour Decoder0.0372020-05-07jacopo pinzinocorrect typo in Endeavour Decoder subsection of the<br>Phase2_FM_specs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |            | Marius Wensing  | adding example waveform for CRFromHost input         |

| 0.0312020-02-20Frans SchreuderFixed some issues in the EndeavourDecoder/Encoder<br>documents (figures not found etc) Unified tables through-<br>out the document0.0322020-02-20Jacopo Pinzinoimprovement endeavour encoder decoder part0.0332020-02-20Frans Schreuderregenerated pdf0.0342020-02-21Frans SchreuderSome minor updates to Endeavour Decoder / Encoder0.0352020-03-17Frans SchreuderAdded section about TTC Encoder0.0362020-05-07jacopo pinzinoadded EndeavourDeglitcher in the Endeavour Decoder<br>subsection of the Phase2_FM_specs0.0372020-05-07jacopo pinzinocorrect typo in Endeavour Decoder subsection of the<br>Phase2_FM_specs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0.029    | 2020-02-17 | Marius Wensing  | starting to document the FromHost Central Router     |

| Image: https://www.communicationImage: https://www.communicationImage: https://www.communicationImage: https://www.communication0.0322020-02-20Jacopo Pinzinoimprovement endeavour encoder decoder part0.0332020-02-20Frans Schreuderregenerated pdf0.0342020-02-21Frans SchreuderSome minor updates to Endeavour Decoder / Encoder0.0352020-03-17Frans SchreuderAdded section about TTC Encoder0.0362020-05-07jacopo pinzinoadded EndeavourDeglitcher in the Endeavour Decoder subsection of the Phase2_FM_specs0.0372020-05-07jacopo pinzinocorrect typo in Endeavour Decoder subsection of the Phase2_FM_specs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0.030    | 2020-02-18 | Marius Wensing  |                                                      |

| Image: constraint of the systemImage: constraint of the systemImage: constraint of the system0.0322020-02-20Jacopo PinzinoImprovement endeavour encoder decoder part0.0332020-02-20Frans Schreuderregenerated pdf0.0342020-02-21Frans SchreuderSome minor updates to Endeavour Decoder / Encoder0.0352020-03-17Frans SchreuderAdded section about TTC Encoder0.0362020-05-07jacopo pinzinoadded EndeavourDeglitcher in the Endeavour Decoder subsection of the Phase2_FM_specs0.0372020-05-07jacopo pinzinocorrect typo in Endeavour Decoder subsection of the Phase2_FM_specs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0.031    | 2020-02-20 | Frans Schreuder |                                                      |

| 0.0322020-02-20Jacopo Pinzinoimprovement endeavour encoder decoder part0.0332020-02-20Frans Schreuderregenerated pdf0.0342020-02-21Frans SchreuderSome minor updates to Endeavour Decoder / Encoder0.0352020-03-17Frans SchreuderAdded section about TTC Encoder0.0362020-05-07jacopo pinzinoadded EndeavourDeglitcher in the Endeavour Decoder subsection of the Phase2_FM_specs0.0372020-05-07jacopo pinzinocorrect typo in Endeavour Decoder subsection of the Phase2_FM_specs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |            |                 |                                                      |

| 0.0332020-02-20Frans Schreuderregenerated pdf0.0342020-02-21Frans SchreuderSome minor updates to Endeavour Decoder / Encoder0.0352020-03-17Frans SchreuderAdded section about TTC Encoder0.0362020-05-07jacopo pinzinoadded EndeavourDeglitcher in the Endeavour Decoder subsection of the Phase2_FM_specs0.0372020-05-07jacopo pinzinocorrect typo in Endeavour Decoder subsection of the Phase2_FM_specs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |            |                 |                                                      |

| 0.0342020-02-21Frans SchreuderSome minor updates to Endeavour Decoder / Encoder0.0352020-03-17Frans SchreuderAdded section about TTC Encoder0.0362020-05-07jacopo pinzinoadded EndeavourDeglitcher in the Endeavour Decoder<br>subsection of the Phase2_FM_specs0.0372020-05-07jacopo pinzinocorrect typo in Endeavour Decoder subsection of the<br>Phase2_FM_specs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |            |                 |                                                      |

| 0.035       2020-03-17       Frans Schreuder       Added section about TTC Encoder         0.036       2020-05-07       jacopo pinzino       added EndeavourDeglitcher in the Endeavour Decoder subsection of the Phase2_FM_specs         0.037       2020-05-07       jacopo pinzino       correct typo in Endeavour Decoder subsection of the Phase2_FM_specs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |            |                 | <b>3</b>                                             |

| 0.036       2020-05-07       jacopo pinzino       added EndeavourDeglitcher in the Endeavour Decoder subsection of the Phase2_FM_specs         0.037       2020-05-07       jacopo pinzino       correct typo in Endeavour Decoder subsection of the Phase2_FM_specs         0.037       2020-05-07       jacopo pinzino       correct typo in Endeavour Decoder subsection of the Phase2_FM_specs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |            |                 |                                                      |

| 0.037     2020-05-07     jacopo pinzino     correct typo in Endeavour Decoder subsection of the Phase2_FM_specs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |            |                 |                                                      |

| Phase2_FM_specs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |            |                 | subsection of the Phase2_FM_specs                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0.037    | 2020-05-07 | jacopo pinzino  |                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0.038    | 2020-05-12 | jacopo pinzino  |                                                      |

| 2020-06-05               | Elena Zhivun                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Started on updating ITk Strips documentation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|